Copyright

by

Xianglong Huang

2006

# The Dissertation Committee for Xianglong Huang certifies that this is the approved version of the following dissertation:

## Improving Program Locality On-the-fly

| Committee:                      |

|---------------------------------|

| Kathryn S. McKinley, Supervisor |

| Stephen M Blackburn             |

| Don Batory                      |

| Douglas C. Burger               |

| Calvin Lin                      |

## Improving Program Locality On-the-fly

$\mathbf{b}\mathbf{y}$

Xianglong Huang, B.S., M.S.

#### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN  ${\rm May} \ 2006$

## Acknowledgments

I am fortunate to meet so many people who have been great help over the years of my graduate school. First I would like to thank my advisor, Kathryn McKinley. She has been an excellent advisor, mentor, guide and friend. I feel really lucky to be her student and to have the privilege of working with her for 6 years. I become a much more capable researcher under her guidance over these years.

I would like to thank my master's advisor, Steve Carr. He is such a wonderful person to work with. Especially during the time when I could not communicate fluently in English, he has been so patient and encouraging. He changed my view of research and because of him, I fell in love with research and decided to pursue my Ph.D. degree.

I can not overstate how important Steve Blackburn is to me on my research. In additional to providing high quality infrastructures and tools for my research, he also taught me a lot of the important principles and skills on programming. Without the help and knowledge I got from him, I will need another 6 years to finish all the work in my dissertation. He is my unofficial co-advisor.

My friends, especially my lunch bunch, Mike, Phoebe, Ben, Sam, Brendon, Emery, and Rich, they helped me over so many difficult times. Especially when I am down, having lunch is the highlight of my day and I enjoyed the

jokes, laughter, or just chatting. Sam, Brendon, and Emery also give me so many useful tips along the way of my Ph.D. study. I will miss my friends so much after I leave Austin.

My beautiful fiancee, Jingyuan (Ada), is my other strong support through the years. She has seen my darkest side, listened to most of my complaints when I feel stressed. She is always a good listener and supporter.

My parents and my sister are among the people who will be happy for me and they made me who I was before I came to the U.S. Without my family, I will never have the opportunity to come to the U.S. to study.

People in or outside my research group, Maria, Peter, Matt, Jenn, and others also give me so much help on my talks and on my written English. I really appreciate those help.

There are numerous people helped me and believed in me through the years. I can not enumerate them all, but I thank them and appreciate what I have got from them. I can not get here without you all helping me.

### Improving Program Locality On-the-fly

Publication No.

Xianglong Huang, Ph.D.

The University of Texas at Austin, 2006

Supervisor: Kathryn S. McKinley

As increases in processor speed continue to outpace increases in cache and memory speed, programs are losing more performance to poor locality. Object-oriented languages exacerbate this problem by adopting new features such as just-in-time (JIT) compilation, dynamic class loading, and many small methods. However, they provide significant software engineering benefits and have become enormously popular. Solutions that bridge the memory gap will combine good performance with fast software development. We found although unique features of object-oriented languages, such as automatic memory management, dynamic compilation, and runtime monitoring systems, generate performance overhead, they also provide new opportunities for online optimizations which are not exploited by previous work. In this thesis, we take advantage of these opportunities with new approaches that improve data and instruction locality at runtime with low overhead.

To improve data locality, we first implement a new dynamic, low overhead, online class analysis to find data locality. Our algorithm detects hot fields for hot objects and then reorders the objects according to their heat on-the-fly in a copying generational collector. The overall time variation between static orderings can be up to 25% and there is no consistent winner. In contrast, our new dynamic class reordering always matches or improves over the best static ordering since its history-based copying order tunes memory layout to program traversal.

To improve instruction locality, we develop two schemes for improving instruction locality in a Java Virtual Machine environment. We first describes a partial code reordering system, which reduces the program instruction working set and cache conflict misses with extremely low overhead. We then present a code management system that uses dynamic profiling to reorder all JIT-compiled code to improve instruction locality with novel efficient algorithms. Both systems show that the VM can dynamically improve instruction locality with little overhead.

These results indicate that the VM layer for modern languages are not just a cost-to-be-borne, but instead open up a new class of optimizations for monitoring and improving data and instruction locality, and code quality. Thus these results point to a future of programming languages that are robust, dependable, and high performance.

## **Table of Contents**

| Ackno             | wledgments                                                                                                                                                  | iv                                           |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Abstra            | act                                                                                                                                                         | vi                                           |

| List of           | Tables                                                                                                                                                      | xi                                           |

| List of           | Figures                                                                                                                                                     | xii                                          |

| 1.1<br>1.2        | er 1. Introduction Improving Data Locality                                                                                                                  | 1<br>3<br>5<br>8                             |

| 2.1<br>2.2<br>2.3 | er 2. Background  Jikes RVM                                                                                                                                 | 11<br>12<br>13<br>15                         |

| 3.1               | er 3. Literature Survey  Memory Performance Studies                                                                                                         | 17<br>17<br>18<br>21<br>21<br>24             |

| 4.1<br>4.2<br>4.3 | er 4. Methodology  Jikes RVM  Dynamic SimpleScalar  DaCapo Benchmarks  4.3.1 Benchmark Characteristics  4.3.2 Program Locality Potential  Server Benchmarks | 27<br>27<br>29<br>30<br>31<br>34<br>35<br>36 |

| 4.5               | Platforms                                                                                                                                                   | - 30                                         |

| Chapte |        | Online Object Reordering to Improve Data Locality 39 |

|--------|--------|------------------------------------------------------|

| 5.1    |        | e Object Reordering Algorithm                        |

|        | 5.1.1  | Static Identification of Field Accesses 40           |

|        | 5.1.2  | Dynamically Identifying Hot Fields 41                |

|        | 5.1.3  | Reordering during Garbage Collection                 |

| 5.2    | Exper  | imental Results                                      |

|        | 5.2.1  | Experimental Platform 45                             |

|        | 5.2.2  | Overhead of Reordering Analysis                      |

|        |        | Class Sensitive vs. Class Oblivious                  |

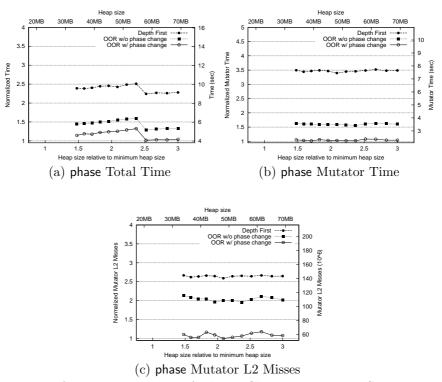

|        |        | Capturing Phase Changes 51                           |

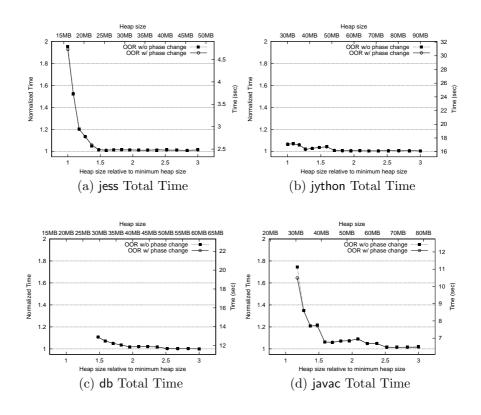

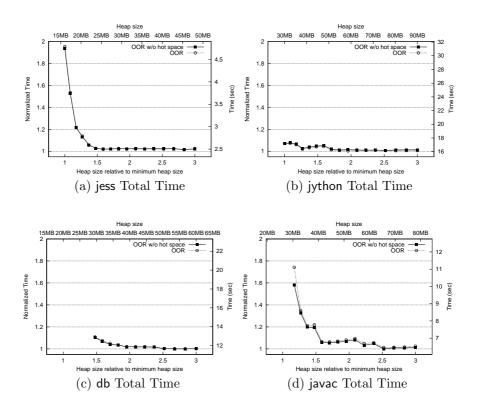

|        | 5.2.5  | Hot Space                                            |

|        |        | Hot Field Analysis                                   |

|        | 5.2.7  | Hot Method Analysis                                  |

| 5.3    | Differ | ent Platforms                                        |

| 5.4    |        | Copying Advantage                                    |

| 5.5    |        | ary                                                  |

| 0.0    | Samm   |                                                      |

| Chapte | er 6.  | Dynamic Systems for Improving Instruction Local-     |

|        | - · ·  | ity 62                                               |

| 6.1    |        | ent Types of Instruction Cache Misses                |

| 6.2    |        | e Program and Incremental Code Layout 66             |

| 6.3    |        | e Program Dynamic Code Management System 67          |

|        | 6.3.1  | Whole Code Management overview                       |

|        | 6.3.2  | WCM Implementation on IA-32 69                       |

|        |        | 6.3.2.1 Current Status                               |

|        |        | 6.3.2.2 Discussion                                   |

|        |        | 6.3.2.3 Alternatives to WCM                          |

|        | 6.3.3  | The Code Layout Algorithms                           |

|        |        | 6.3.3.1 Pettis-Hansen Algorithm                      |

|        |        | 6.3.3.2 Cache-Aware Pettis-Hansen Algorithm 76       |

|        |        | 6.3.3.3 Code Tiling Algorithm                        |

|        |        | 6.3.3.4 Linear Scan Algorithm 80                     |

|        | 6.3.4  | WCM Results                                          |

|        |        | 6.3.4.1 Experimental framework 81                    |

|        |        | 6.3.4.2 WCM Overhead                                 |

|        |        | 6.3.4.3 WCM Performance Results 86                   |

|        |        | 6.3.4.4 Discussion                                   |

|        | 6.3.5  | PMU-based Code Reorganization 89                     |

|        | 2.0.0  | 6.3.5.1 Experimental Framework                       |

|        |        | 6.3.5.2 PMU-based DCG Generation Overhead 90         |

|        |        | 6.3.5.3 Code reorganization results                  |

|        |        | 6.3.5.4 Effectiveness of PMU sampling                |

|        |        | 6.3.5.5 Discussion                                   |

| 6.4    | Fast a | and Efficient Partial Online Code Reordering         |

| 0.1    |        | Partial Code Reordering                              |

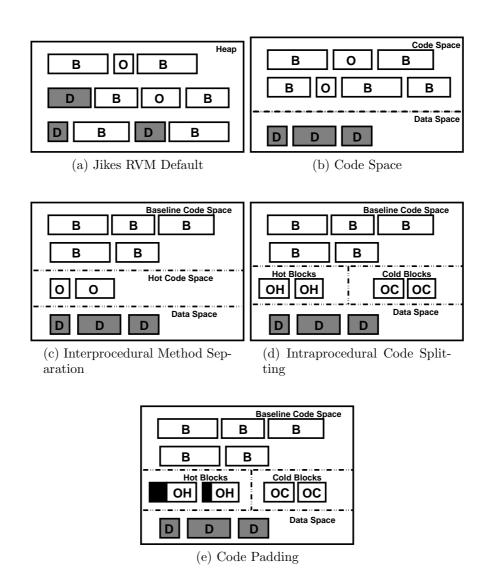

|                  |        | 6.4.1.1 Interprocedural Method Separation                | 99                |

|------------------|--------|----------------------------------------------------------|-------------------|

|                  |        | 6.4.1.2 Intraprocedural Code Splitting                   | 99                |

|                  |        | 6.4.1.3 Code Padding                                     | 100               |

|                  | 6.4.2  | Experimental Results                                     | 102               |

|                  |        | 6.4.2.1 Application and Compiler Mix                     | 103               |

|                  |        | 6.4.2.2 Benchmarks and Instruction Code Sizes            | 104               |

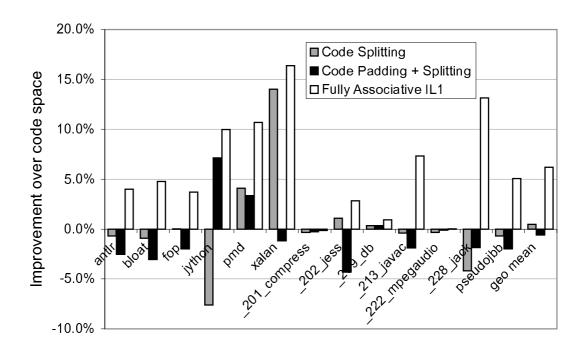

|                  |        | 6.4.2.3 Simulation Results                               | 105               |

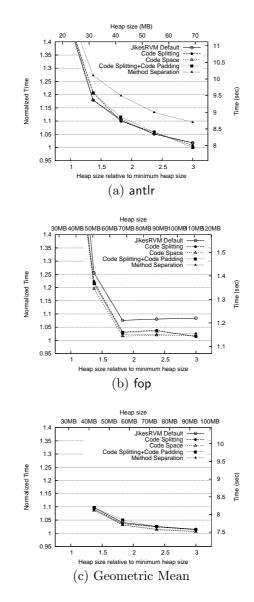

|                  |        | 6.4.2.4 Application Performance                          | 109               |

|                  |        | 6.4.2.5 Mix of Compiler and Application                  | 111               |

|                  | Addin  | Applicability of Results to Other VMs g OOR to Other VMs | 116<br>117<br>117 |

| Chapte           | er 8.  | Conclusions and Future Work                              | 119               |

|                  |        | e Work                                                   | 120               |

|                  | 8.1.1  | Performance Counters                                     | 121               |

|                  | 8.1.2  | Potential Applications of Dynamic Monitoring             | 122               |

| Bibliog          | graphy |                                                          | 124               |

| $\mathbf{Index}$ |        |                                                          | 136               |

| Vita             |        |                                                          | 137               |

## List of Tables

| 4.1 | Benchmark Characteristics With Adaptive Run                   | 32  |

|-----|---------------------------------------------------------------|-----|

| 4.2 | Benchmark Characteristics With Fixed Workload                 | 33  |

| 4.3 | Benchmark characteristics                                     | 36  |

| 5.1 | OOR System Overhead                                           | 47  |

| 6.1 | Number of Conflict Misses $(10^7)$                            | 65  |

| 6.2 | Breakdown of time to reorganize MiniBean's code (ms)          | 72  |

| 6.3 | Benchmark characteristics                                     | 82  |

| 6.4 | MiniBean and SPEC JBB2000 layout creation times (ms)          | 84  |

|     | IPF front-end stalls using static code layout                 | 93  |

|     | Benchmark Code Size Characteristics in Bytes with Replay Com- |     |

|     | pilation                                                      | 102 |

## List of Figures

|                                                                                                                                             | Java programs with Perfect Caches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 4.1                                                                                                                                         | Java Benchmarks with Perfect Caches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35                                                                   |

| 5.1                                                                                                                                         | OOR System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40                                                                   |

| 5.2                                                                                                                                         | Pseudocode for Decaying Field Heat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 42                                                                   |

| 5.3                                                                                                                                         | Pseudocode for Advice Based Copying                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45                                                                   |

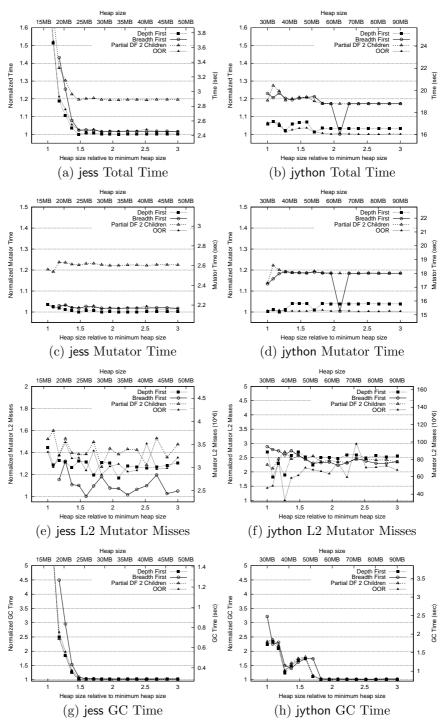

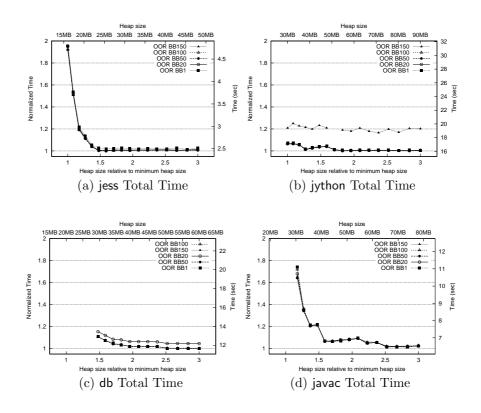

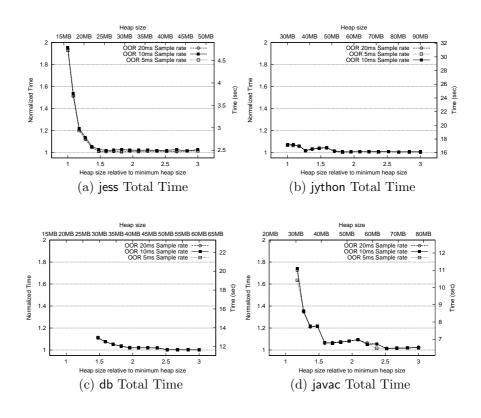

| 5.4                                                                                                                                         | OOR vs. Class-Oblivious Traversals [jess & jython]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48                                                                   |

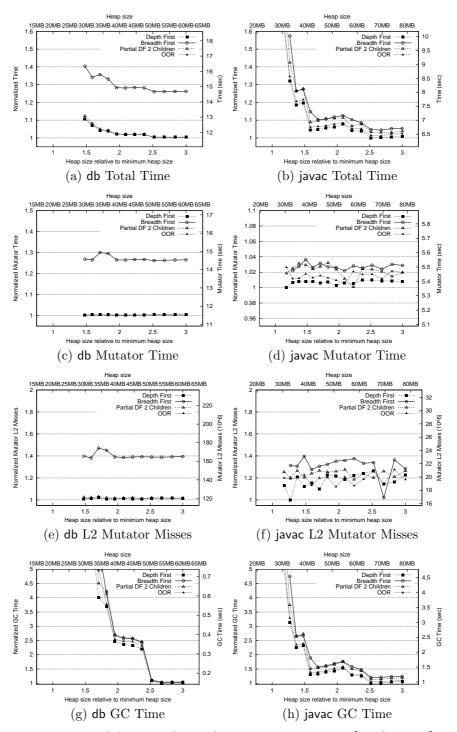

| 5.5                                                                                                                                         | OOR vs. Class-Oblivious Traversals [db & javac]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50                                                                   |

| 5.6                                                                                                                                         | Performance Impact of Phase Changes Using a Synthetic Bench-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

| _                                                                                                                                           | mark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52                                                                   |

| 5.7                                                                                                                                         | Absence of Phasic Behavior in Standard Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53                                                                   |

| 5.8                                                                                                                                         | OOR without Hot Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54                                                                   |

| 5.9                                                                                                                                         | Using Different Policies to Determine Cold Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 55                                                                   |

|                                                                                                                                             | Using Different Policies to Determine Hot Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 56                                                                   |

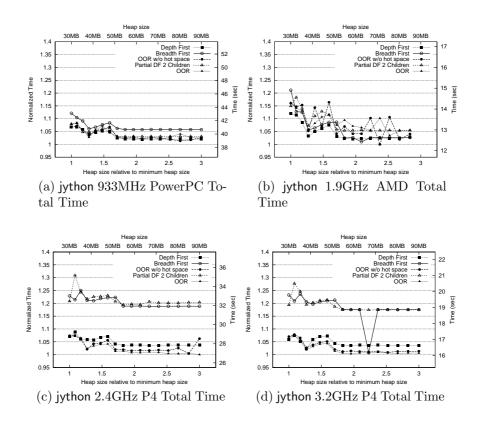

|                                                                                                                                             | Performance on Different Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 58                                                                   |

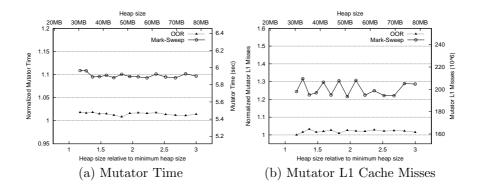

|                                                                                                                                             | Mutator Performance for Copying and Mark-Sweep Collectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00                                                                   |

| J.12                                                                                                                                        | on javac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 59                                                                   |

| 5.13                                                                                                                                        | Garbage Collection vs. Idealized Mark-Sweep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61                                                                   |

|                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                      |

| 6.1                                                                                                                                         | Instruction L1 vs. Data L1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64                                                                   |

| 6.1<br>6.2                                                                                                                                  | Instruction L1 vs. Data L1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64<br>65                                                             |

| 6.2                                                                                                                                         | Direct-mapped vs. Fully Associative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 65                                                                   |

| 6.2<br>6.3                                                                                                                                  | Direct-mapped vs. Fully Associative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 65<br>69                                                             |

| 6.2<br>6.3<br>6.4                                                                                                                           | Direct-mapped vs. Fully Associative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 65<br>69<br>76                                                       |

| 6.2<br>6.3<br>6.4<br>6.5                                                                                                                    | Direct-mapped vs. Fully Associative  Whole Code Management  Pettis-Hansen procedure layout algorithm  Cache-Aware Pettis-Hansen algorithm                                                                                                                                                                                                                                                                                                                                                                                                      | 65<br>69<br>76<br>77                                                 |

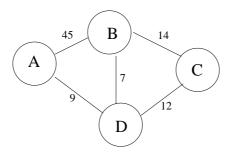

| 6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                                                                             | Direct-mapped vs. Fully Associative Whole Code Management Pettis-Hansen procedure layout algorithm Cache-Aware Pettis-Hansen algorithm An example dynamic call graph                                                                                                                                                                                                                                                                                                                                                                           | 65<br>69<br>76<br>77<br>78                                           |

| 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                                                                                      | Direct-mapped vs. Fully Associative Whole Code Management Pettis-Hansen procedure layout algorithm Cache-Aware Pettis-Hansen algorithm An example dynamic call graph Code Tiling algorithm                                                                                                                                                                                                                                                                                                                                                     | 65<br>69<br>76<br>77<br>78<br>79                                     |

| 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                                                                                               | Direct-mapped vs. Fully Associative Whole Code Management Pettis-Hansen procedure layout algorithm Cache-Aware Pettis-Hansen algorithm An example dynamic call graph Code Tiling algorithm Linear Scan algorithm                                                                                                                                                                                                                                                                                                                               | 65<br>69<br>76<br>77<br>78<br>79<br>81                               |

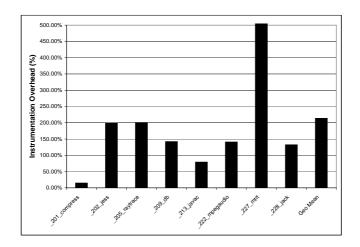

| 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9                                                                                        | Direct-mapped vs. Fully Associative Whole Code Management Pettis-Hansen procedure layout algorithm Cache-Aware Pettis-Hansen algorithm An example dynamic call graph Code Tiling algorithm Linear Scan algorithm SPEC JVM98 software instrumentation overheads                                                                                                                                                                                                                                                                                 | 65<br>69<br>76<br>77<br>78<br>79<br>81<br>84                         |

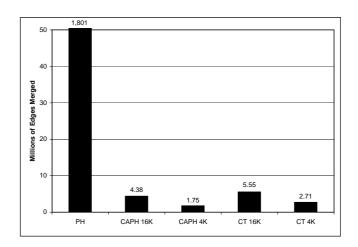

| 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10                                                                                | Direct-mapped vs. Fully Associative Whole Code Management Pettis-Hansen procedure layout algorithm Cache-Aware Pettis-Hansen algorithm An example dynamic call graph Code Tiling algorithm Linear Scan algorithm SPEC JVM98 software instrumentation overheads Number of edge merges for MiniBean                                                                                                                                                                                                                                              | 65<br>69<br>76<br>77<br>78<br>79<br>81<br>84<br>85                   |

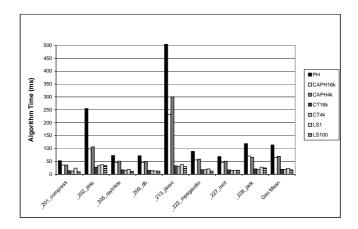

| 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11                                                                        | Direct-mapped vs. Fully Associative Whole Code Management Pettis-Hansen procedure layout algorithm Cache-Aware Pettis-Hansen algorithm An example dynamic call graph Code Tiling algorithm Linear Scan algorithm SPEC JVM98 software instrumentation overheads Number of edge merges for MiniBean SPEC JVM98 layout generation times (ms)                                                                                                                                                                                                      | 65<br>69<br>76<br>77<br>78<br>79<br>81<br>84<br>85<br>86             |

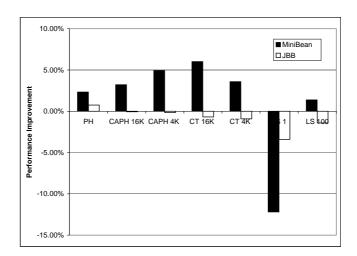

| 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12                                                                | Direct-mapped vs. Fully Associative Whole Code Management Pettis-Hansen procedure layout algorithm Cache-Aware Pettis-Hansen algorithm An example dynamic call graph Code Tiling algorithm Linear Scan algorithm SPEC JVM98 software instrumentation overheads Number of edge merges for MiniBean SPEC JVM98 layout generation times (ms) MiniBean and SPEC JBB2000 performance                                                                                                                                                                | 65<br>69<br>76<br>77<br>78<br>79<br>81<br>84<br>85<br>86<br>87       |

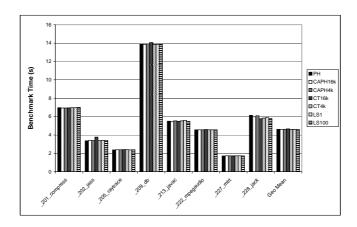

| 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.11<br>6.12<br>6.13                                                                | Direct-mapped vs. Fully Associative Whole Code Management Pettis-Hansen procedure layout algorithm Cache-Aware Pettis-Hansen algorithm An example dynamic call graph Code Tiling algorithm Linear Scan algorithm SPEC JVM98 software instrumentation overheads Number of edge merges for MiniBean SPEC JVM98 layout generation times (ms) MiniBean and SPEC JBB2000 performance SPEC JVM98 performance                                                                                                                                         | 65<br>69<br>76<br>77<br>78<br>79<br>81<br>84<br>85<br>86<br>87       |

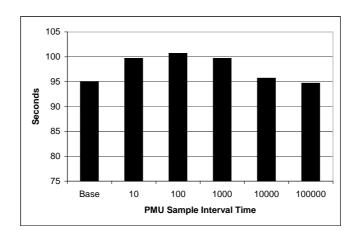

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \\ 6.12 \\ 6.13 \\ 6.14 \end{array}$                 | Direct-mapped vs. Fully Associative Whole Code Management Pettis-Hansen procedure layout algorithm Cache-Aware Pettis-Hansen algorithm An example dynamic call graph Code Tiling algorithm Linear Scan algorithm SPEC JVM98 software instrumentation overheads Number of edge merges for MiniBean SPEC JVM98 layout generation times (ms) MiniBean and SPEC JBB2000 performance SPEC JVM98 performance MiniBean DCG creation times with PMU sampling                                                                                           | 65<br>69<br>76<br>77<br>78<br>79<br>81<br>84<br>85<br>86<br>87<br>88 |

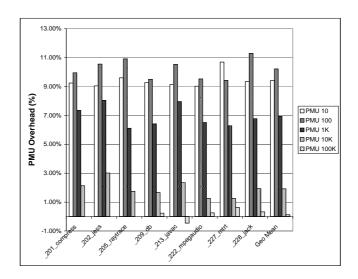

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \\ 6.12 \\ 6.13 \\ 6.14 \\ 6.15 \end{array}$         | Direct-mapped vs. Fully Associative Whole Code Management Pettis-Hansen procedure layout algorithm Cache-Aware Pettis-Hansen algorithm An example dynamic call graph Code Tiling algorithm Linear Scan algorithm SPEC JVM98 software instrumentation overheads Number of edge merges for MiniBean SPEC JVM98 layout generation times (ms) MiniBean and SPEC JBB2000 performance SPEC JVM98 performance SPEC JVM98 performance MiniBean DCG creation times with PMU sampling PMU overhead for the SPEC JVM98 benchmarks                         | 65<br>69<br>76<br>77<br>78<br>79<br>81<br>84<br>85<br>86<br>87<br>88 |

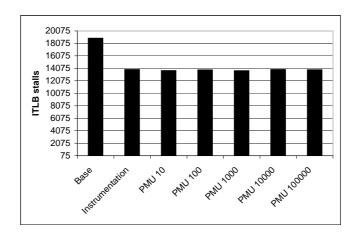

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \\ 6.12 \\ 6.13 \\ 6.14 \\ 6.15 \\ 6.16 \end{array}$ | Direct-mapped vs. Fully Associative Whole Code Management Pettis-Hansen procedure layout algorithm Cache-Aware Pettis-Hansen algorithm An example dynamic call graph Code Tiling algorithm Linear Scan algorithm SPEC JVM98 software instrumentation overheads Number of edge merges for MiniBean SPEC JVM98 layout generation times (ms) MiniBean and SPEC JBB2000 performance SPEC JVM98 performance MiniBean DCG creation times with PMU sampling PMU overhead for the SPEC JVM98 benchmarks Effect of PMU-based call graphs on ITLB misses | 65<br>69<br>76<br>77<br>78<br>79<br>81<br>84<br>85<br>86<br>87<br>88 |

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \\ 6.12 \\ 6.13 \\ 6.14 \\ 6.15 \\ 6.16 \end{array}$ | Direct-mapped vs. Fully Associative Whole Code Management Pettis-Hansen procedure layout algorithm Cache-Aware Pettis-Hansen algorithm An example dynamic call graph Code Tiling algorithm Linear Scan algorithm SPEC JVM98 software instrumentation overheads Number of edge merges for MiniBean SPEC JVM98 layout generation times (ms) MiniBean and SPEC JBB2000 performance SPEC JVM98 performance SPEC JVM98 performance MiniBean DCG creation times with PMU sampling PMU overhead for the SPEC JVM98 benchmarks                         | 65<br>69<br>76<br>77<br>78<br>79<br>81<br>84<br>85<br>86<br>87<br>88 |

| 6.18 | Pseudocode for Code Padding                                    | 101 |

|------|----------------------------------------------------------------|-----|

| 6.19 | Simulation Results for Directed-Mapped and Fully Associative   |     |

|      | 32 KB IL1, 512 KB L2                                           | 106 |

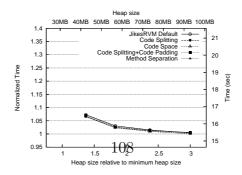

| 6.20 | Code Optimizations on Pentium 4                                | 108 |

| 6.21 | Code Optimizations on PowerPC 970: Geometric Mean              | 108 |

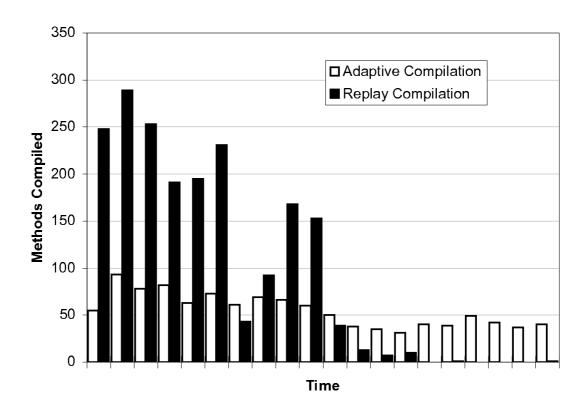

| 6.22 | Compiler Activity Histogram on First Iteration                 | 110 |

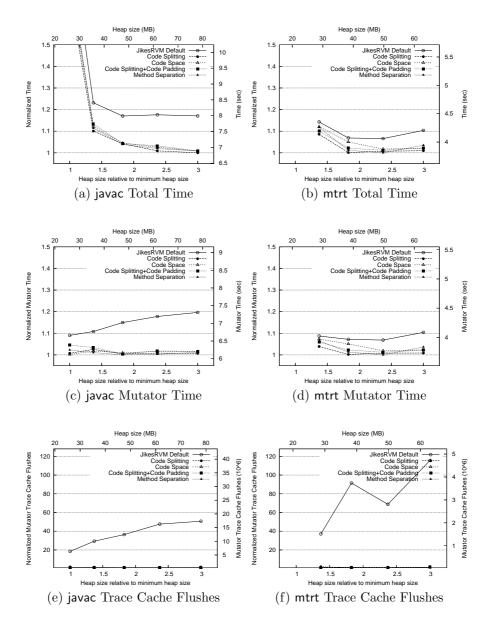

| 6.23 | Total time, mutator time, and trace cache flushes for a simple |     |

|      | code cache, Jikes RVM default and various PCR configurations.  | 112 |

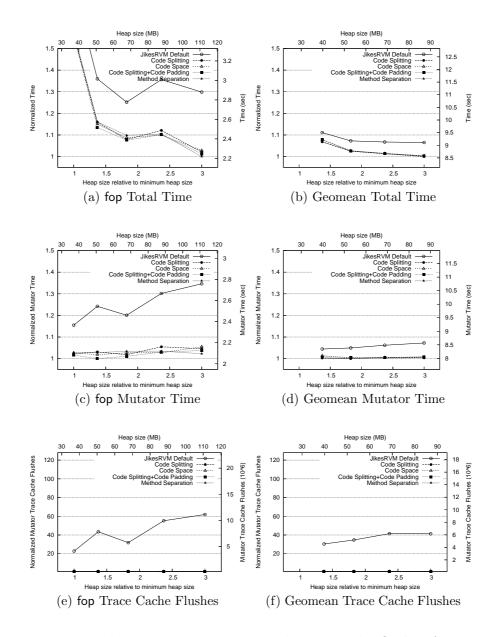

| 6.24 | Total time, mutator time, and trace cache flushes for a simple |     |

|      | code cache, Jikes RVM default and various PCR configurations.  | 113 |

|      |                                                                |     |

## Chapter 1

## Introduction

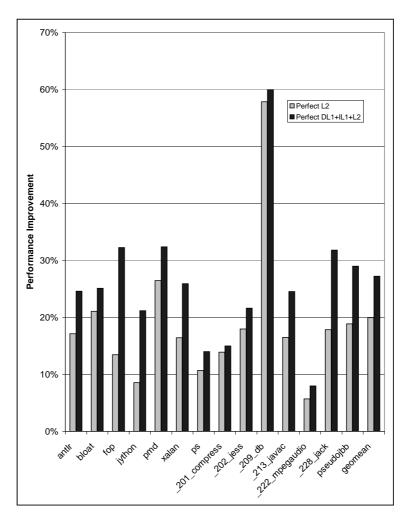

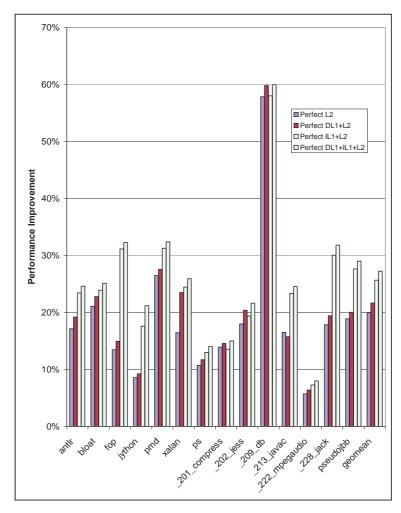

Due to wire scaling and clock rates, processors will soon only be able to access a fraction of the chip in one cycle. This trend will result in (1) partitioning of some components such as caches and register files, (2) longer latency to access the memory and more complex memory systems, and (3) multi-core architectures which will need to find and exploit more instruction level parallelism (ILP) for performance. The imbalance between memory and processor speeds is called the memory gap. The memory gap is already a serious performance bottleneck and could be getting worse because of the new hardware technologies. Software can help alleviate the memory gap by improving data and instruction locality and can consequently reduce long latency memory accesses. But the popular object-oriented programming languages, such as Java and C#, still lose significant performance due to poor locality. We measure the potential locality improvements for nine Java programs, and we find these programs spend on average 27% of their execution time waiting for cache misses from L1 and L2 in Figure 1.1 (see Section 4.3.2 for detailed analysis).

The goals of good software engineering and high performance are often at odds. Common wisdom holds that object-oriented languages offer software engineering benefits such as fewer errors and reduced development time, but

Figure 1.1: Java programs with Perfect Caches

these languages do so at a cost: New features such as garbage collection, JIT (just-in-time) compilation, and dynamic class binding add performance overhead to programs. Common wisdom also holds that traditional programming languages such as C offer performance benefits at a software engineering cost. With effort, programmers can free memory as soon as possible and use specialized allocators to gain memory efficiency and speed. For instruction accesses,

C has pre-compiled and pre-allocated instructions which eliminate the runtime overhead of dynamic code generation. However, C has a hidden performance cost. Because C cannot move objects and instructions without violating language semantics, it requires a non-moving allocator, such as one based on free lists. A free-list allocator places contemporaneously-allocated objects in whichever locations are free at that time, but these locations are not necessarily adjacent or even nearby in memory. Java can move objects and can thus use contiguous allocation to attain locality for contemporaneously-allocated objects and instructions, and Java can use copying collection to place objects and instructions with locality closer together, or even move objects and instructions. These dynamic optimization opportunities have not been exploited by previous research.

Our approach to improving program locality is to exploit the available opportunities in object-oriented program languages to generate powerful dynamic optimizations to improve program locality with low overhead. The programs thus can potentially achieve better data and instruction locality than programs written in traditional programming languages.

## 1.1 Improving Data Locality

There has been a lot of research on compile time optimizations for array accesses inside loops to improve data locality [17, 18, 33, 35, 43, 54]. Object-oriented languages usually use more pointer data structures than traditional programming languages and previous approaches only solve a small part of

the problems.

Copying generational collection is one of the best performing memory managers [11]. The allocator places contemporaneously allocated objects in contiguous memory. Generational copying collectors divide objects into newly allocated nursery objects and objects that have survived one or more collections [5, 51, 67]. Because most objects die young and the nursery is collected separately, generational copying collectors have better performance than nongenerational collectors [5, 11]. Copying collectors promote reachable objects using transitive closure and place objects in breadth first [21] or depth first order [48,69]. Prior research to improve data locality by changing copying orders has explored priori static orderings [48,69], static class profiling [22,61], and online object instance sampling [24]. Static orderings are problematic when program traversal patterns do not match the collector's single ordering. We show large differences ranging of up to 25% in total execution time due to the locality of static copy orders for some benchmarks. In a JIT (just-intime) optimizing compiler for Java, dynamic class loading provides more nondeterminism and therefore limits the generality of static profiling. Instance based reordering is potentially more powerful than the class based orderings we present, since objects with locality are not necessarily connected. However, the sampling space and time overheads for just the old objects are significant (6% in time for Cecil [24]) and miss the opportunity to improve locality when the collector promotes young (nursery) objects.

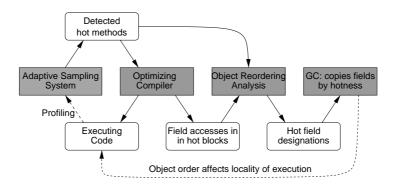

We introduce a novel low-cost dynamic class analysis that drives a gen-

erational [67] copying collector to use copy orders that match data access patterns and thus improve data locality. Our online class reordering analysis achieves its low cost (at most 2\% of total time) by piggybacking on method sampling in an adaptive JIT compiler. The adaptive compiler in Jikes RVM uses timer-driven sampling to identify hot (frequently executed) methods, and they adaptive compiler recompiles them at progressively higher optimization levels. At compile time, online class analysis enumerates the field accesses in each method. During execution, when the adaptive compiler identifies a hot method (regardless of its optimization choice), adaptive class reordering analysis marks the fields the method accesses as hot. At garbage collection time, the collector preferentially copies referents of hot fields first, together with their parent. In this framework, we explore how quickly to decay heat to respond to phase changes, exploit Jikes RVM's static analysis to exclude cold basic blocks from the reordering analysis, and group objects of hot classes together in a separate copy space. More details about this research are presented in Chapter 5.

### 1.2 Improving Instruction Locality

Another locality problem is instruction locality. Previous research on code reordering usually uses static profiling to perform reordering either at compile time or at link time, which as we point out above is problematic for Java. Most studies try to reorder code on three different granularities, procedure reordering [36, 37, 58], basic block reordering [37, 58, 59], or proce-

dure splitting [58]. Their results show improvement in reducing instruction cache misses by up to 40% [37]. Because Java virtual machines have dynamic class loading and dynamic code generation, these static schemes are less effective. However, Java virtual machines also provide a new opportunity to apply similar optimizations during the execution of the program. We can pick the most frequently executed methods and avoid conflict misses on these methods. Most previous dynamic schemes include hardware components for detecting and removing conflict misses [10, 60]. Chen et al. [20] dynamically allocate procedure code at the time the procedure is invoked. But they only reorder the procedures inside libraries and they cannot move the instructions after they have been allocated. They show a comparable benefit to the profile-based algorithms.

We developed two online code reordering systems for improving instruction locality: one reorders all the methods in the heap and the other only does partial code reordering. An advantage of online schemes is that they can accommodate the dynamic properties of Java programs such as dynamic class loading, garbage collection, and dynamic code generation. However, the overhead at run time needs to be low to make our online algorithms beneficial.

We first describe the implementation of a Whole Code Management (WCM) system that is integrated into our managed runtime in Section 6.3. WCM uses dynamic profile information to reorganize all the compiled code at the granularity of a method. We show that our WCM can significantly improve performance. We also describe three new procedure layout algorithms that,

compared to previous approaches, reduce the cost of computing a new code placement. These algorithms specifically target ITLB misses, which typically have the greatest impact on performance because of their frequency and high cost. One of these algorithms, the Code Tiling is significantly faster both in worst case complexity and in practice than the best-known previous technique by Pettis and Hansen [58]. We demonstrate that Code Tiling generates code layouts that are better or comparable to those by the Pettis-Hansen algorithm.

Although our WCM algorithms have much lower overhead than the popular Pettis-Hansen algorithm, they are still too expensive for short running programs. We hence developed Partial Code Reordering (PCR) which performs partial online code reordering so that we achieve even lower low overhead than WCM. PCR improves instruction locality by attacking both capacity misses and conflict misses in the cache. PCR performs three optimizations using multiple code spaces: (1) interprocedural hot/cold method separation, (2) intraprocedural hot/cold code splitting, and (3) interprocedural hot code padding. To reduce capacity misses, PCR allocates hot and cold methods into separate spaces in the heap. PCR also performs code splitting of hot and cold basic blocks within the same method to further reduce the hot instruction working set size. PCR utilizes the adaptive sampling system in Jikes RVM to detect hot methods and collect the dynamic edge profile to determine hot basic blocks. To reduce conflict misses, PCR uses the dynamic call graph generated by dynamic stack profiling to find hot caller/callee pairs. If the hot caller and callee methods map to the same cache line in the cache,

they will have too many conflict misses. Therefore, PCR applies code padding on either caller or callee method (which ever it happens to be recompiling) to eliminate the potential conflict misses. Detailed algorithms of PCR are presented in Section 6.4.

#### 1.3 Contributions

The main contributions of this thesis are:

1. Program characteristics study: Quantifying Java program memory behavior to find performance losses due to poor locality.

#### 2. Improving data locality:

- (a) A novel, low-overhead, Online Object Reordering (OOR) system to improve data locality. We can improve over static copying orders by up to 25%, and the overhead of OOR is at most 2%.

- (b) A thorough evaluation on three architectures of the performance improvements of data reordering optimizations and the comparison of different static data copying schemes.

#### 3. Improving instruction locality:

(a) A Whole Code Management (WCM) system. This implementation of dynamic code reordering in a managed runtime is the first to our knowledge. Since it operates on-the-fly, it naturally copes with dynamic features of languages like Java such as method recompilation and dynamic class loading. Results show, for example, that it reduces the execution time for a large benchmark by 6%.

- i. A new code placement algorithm called Code Tiling. This algorithm is fast enough to make dynamic code reorganization practical in a high-performance managed runtime. Placements computed by this algorithm perform as well and often better than those produced by the Pettis-Hansen procedure layout algorithm.

- ii. Detailed evaluation of the quality and overhead of dynamic call graphs which are generated using hardware performance counters on Intel Itanium architectures.

- (b) An instruction locality optimization framework, Partial Code Reordering (PCR) system, which piggybacks on hotspot recompilation to achieve negligible overheads and reduced instruction cache footprints.

- i. The design of four code space optimizations: (1) one space with all code<sup>1</sup>; (2) two spaces: separate hot and cold methods; (3) three spaces: cold methods, hot blocks of hot methods, and cold blocks of hot methods; (4) three spaces with method padding for hot caller-callee pairs.

<sup>&</sup>lt;sup>1</sup>This design is common in commercial VMs.

ii. A thorough evaluation on two architectures and in simulation of the potential and actual performance of code space optimizations. Simulation results show potential improvements are possible, but PCR has a negligible effect in practice because of the small instruction cache footprint of the benchmarks we tested.

This work is the first to exploit the available opportunities in objectoriented programming languages to improve program locality with low overhead dynamic optimizations. This dissertation not only proves the applicability of this approach, but also develops several novel dynamic optimizations which effectively improve data and instruction locality.

## Chapter 2

## Background

This chapter gives the background of the two dynamic optimization systems we use in this dissertation. However, our techniques are not specific to these systems and can be added to any systems with mechanisms to identify hot methods at runtime, dynamic code generation, and generational copying collector. All three features are common to current virtual machine systems for Java and C#. Our optimizations for improving program locality are taking advantage of opportunities that are not VM dependent.

We first describe how the adaptive sampling, compilation system, and code allocation in the IBM Jikes RVM [3,4] works. Then we describe the generational copying collector from the Memory Management Toolkit (MMTk). Last, we describe the code generation in Intel Open Runtime Platform virtual machine (ORP) [25] because we implement two different code reordering systems in Jikes RVM and ORP respectively. This chapter is to set the stage to explain our online data/instructions reordering algorithms in the subsequent chapters.

#### 2.1 Jikes RVM

Jikes RVM [4, 6, 7, 44] is an open source high-performance Java-in-Java virtual machine (VM) written almost entirely in a slightly extended Java. A few C code is needed for boot strapping and system calls. Our work of online object reordering and partial code reordering is in the context of Jikes RVM. We leverage the existing adaptive optimization system in Jikes RVM for both our data object reordering and code reordering system. In this section we briefly review the most relevant aspects of this adaptive optimization system.

Jikes RVM does not have a bytecode interpreter. Instead, a fast template-driven baseline compiler produces machine code when the VM first executes each Java method. Using timer-based profiling, the adaptive system periodically samples the currently executing code and records (1) the currently executing method and (2) the caller of the currently executing method. This profile data is fed into a cost-benefit model to identify methods that should be recompiled at a higher level of optimization. Methods selected by the system for recompilation are compiled asynchronously on a separate compilation thread by the Jikes RVM optimizing compiler. The profiled caller-callee relationships are used to maintain a weighted dynamic call graph that drives profile-directed inlining during optimizing compilation.

While generating code, the baseline compiler inserts instrumentation for every bytecode-level conditional branch to measure its execution frequency and its taken/not-taken distribution. The optimizing compiler uses this edge profile data to compute basic block frequencies and branch probabilities. A

number of optimizations exploit this information, and most relevant research to our work is basic block layout generation. At the lowest optimization level (O0), the compiler simply moves infrequently executed basic blocks to the bottom of the compiled method's code. At O1 and O2, it employs Pettis-Hansen's bottom-up positioning algorithm (Algo2) [58]. Note the Pettis-Hansen algorithm used here is for blocks reordering within a method, not the Pettis and Hansen algorithm which does inter-procedural method reordering and will be used for comparison in our instruction locality work.

#### 2.2 Garbage Collection and MMTk

MMTk is an efficient, composable Java memory management toolkit used in Jikes RVM that implements a wide variety of high performance garbage collectors that reuse shared components [11, 12]. It is ideal for our experiments because we can easily apply different algorithms on the same data structure to systematically compare different policies.

We use the copying generational collection in MMTk, which is one of the best performing memory managers [11]. Copying generational collection divides the heap into two portions, a nursery containing newly allocated (i.e., young) objects, and a mature space, containing older objects [51,67]. It further divides the mature space into two semispaces. It collects the nursery frequently (whenever the nursery fills up), by performing a transitive closure over the nursery objects, and copying them into one semispace of the mature space. When that semispace is full after a nursery collection, it copies reachable mature objects into the other semispace and flips the roles of the two semispaces.

Since the generational collector collects the nursery separately from the mature space, it requires the compiler to insert write-barrier code, which at run time records stores of pointers from mature to nursery objects in a remembered set. When the collector starts a nursery GC, the remembered set forms part of the set of root pointers, which also includes the stacks, registers, and static variables. It assumes all reachable objects are live. It copies any referents of the root pointers that lie in the nursery and iteratively enumerates the pointers in newly copied objects, copying their nursery referents, until it copies all reachable nursery objects. Mature space garbage collection proceeds similarly, except the remembered set is empty and the collector copies any reachable objects in both mature space and nursery. This scheme generalizes to multiple generations, but we use two.

We use the bounded generational copying collector (GenCopy) in our Online Object Reordering system for improving data locality. It follows Appel's flexible nursery [5], which shrinks the nursery as mature space occupancy grows, except that we never allow the nursery to exceed a fixed chosen bound (4MB) to reduce the average time to collect the nursery. When mature space occupancy approaches the maximum total heap size, bounded generational collector copying collector shrinks the nursery, until it reaches a lower bound (256KB) that triggers mature space collection. MMTk manages large objects (8KB or bigger) separately in a non-copying space and puts the compiler and a

few other system pieces into the boot image, an immortal space. See Blackburn et al. for additional implementation details [11, 12].

#### 2.3 ORP: Intel Open Runtime Platform

Besides Jikes RVM, we also implemented our optimizations for improving instruction locality in Intel's Open Runtime Platform virtual machine (ORP). ORP is a managed runtime environment that supports Java and C# programs. ORP is more robust than Jikes RVM and ORP can run more benchmarks including large server benchmarks. Not like Jikes RVM, ORP is written in C++. Our core platform consists of the ORP and one or more JIT compilers. On IA-32, we use the optimizing O3 JIT [26] to compile JVM bytecodes. This JIT performs inlining, a number of global optimizations (e.g., copy propagation, dead code elimination, loop transformations, and constant folding), as well as CSE and array bounds check elimination.

In ORP, a JIT may emit compiled code for a method that consists of more than one separately-allocated *code block*, which is a set of basic blocks in one method. Because of this, code blocks are the units of code management in our algorithm, not methods, and WCM reorders code blocks. ORP also allocates code blocks in a region of memory that is separate from the garbage collected heap. It provides different subregions for code that is cold (infrequently executed) and warm (more often executed). ORP allocates code of equal "temperature" sequentially. ORP can collect dynamic profile information from either software instrumentation or from hardware Performance

Monitoring Unit (PMU) sampling. These dynamic profiles are used for optimizations such as basic block reordering within a method.

## Chapter 3

## Literature Survey

In this section, we discuss the most closely related work in the following areas: (1) memory performance studies for Java programs, (2) research on improving data locality for Java, and (3) research on code reordering to generate better instruction locality.

## 3.1 Memory Performance Studies

Several studies characterize the memory behavior and performance of Java programs via simulation [46, 50, 63]. Kim et al. [46] studied memory behavior by feeding Java memory access traces to cache simulators. The garbage collection algorithm they studied was mark-sweep GC. In our study, we will examine the behavior of Java programs in the context of bounded copying nursery generational garbage collectors, which have higher performance [11]. Their study concentrated on data locality but not instruction locality, while our work studies the effect of locality from both caches.

Li et al. [50] studied the performance characteristics of the SPECjvm98 Java programs. They used SimOS in their experiments. They did not differentiate the impact of mutator and GC, which, as we will show later, exhibit very different memory behaviors. SimOS does not have a cycle-level processor model, affecting the accuracy of their results. Also, they did not have detailed study of instruction cache locality.

Shuf et al. [63] use a very similar methodology to Kim et al. They generated traces and simulated memory behavior by using the trace on a cache simulator on some of the benchmarks that we use. They adopted a very large heap size, ignoring the costs and benefits of GC. Also, because they use unusually large heaps, their results focus unnecessarily on TLB misses as a problem. In our study, we vary heap sizes and study the effects of GC and the interaction between mutator and GC. We find these applications very rarely stress the TLB since copying GC usually reduces the program's memory footprint.

## 3.2 Data Locality

The key investigations of our data locality work are (1) exploiting the object reordering that happens during copying generational garbage collection [51, 67], and (2) using online profiling to collect information for controlling the copying order. Much previous research in this area considers non-garbage collected languages (such as C) [22, 23, 69], or does not address the effects of copying collectors [47]. In other words, it neither considers nor exploits moving heap objects.

The related work most pertinent to ours falls into two categories: techniques that group objects to improve *inter*-object locality [22, 24, 48, 69], and those that reorder fields within an instance to improve *intra*-object local-

ity [22,47]. This prior work relies on static analysis or offline profiling to drive object layout decisions and is class-oblivious for the most part, i.e., it treats all classes the same.

One can improve inter-object locality by clustering together objects whose accesses are highly correlated. The work in this area differs in how to define correlation and specific methods to cluster objects. Wilson et al. describe a hierarchical decomposition algorithm to group data structures of LISP programs using static-graph reorganization to improve locality of memory pages [69]. They found that using a two-level queue for the *Cheney scan* groups objects effectively. Lam et al. later conclude that hierarchical decomposition is not always effective [48]. They suggest that users supply object type information to group objects. We automatically and adaptively examine fine-grained field accesses to generate such type-based advice.

Chilimbi and Larus use a continuously running online profiling technique to track recently referenced objects and build a temporal affinity graph [24] based on the frequency of accesses to pairs of objects within a temporal interval. The object pair need not be connected by a pointer, but must lie in the same non-nursery generation to reduce overhead. Their dynamic instance-level profiling records in a buffer most pointers fetched from the heap. They report overheads of 6% for Cecil, a language which is not as well adopted as Java. Exploiting the timer-driven sampling, already in the adaptive optimization system of Jikes RVM, is much cheaper. We find copying cannot guarantee to improve every program by at least 6% so as to overcome instance

profiling costs by their approach. Their algorithm copies together objects with high affinity only during collection of the old generation whereas our system reorders objects during both nursery and old generation collections.

Chilimbi et al. split objects into hot and cold parts to group the hot parts together [22]. This technique is not fully automated and requires substantial programmer intervention. Chilimbi et al.'s clustering and coloring methods also rely on manual insertion of special allocation functions [23]. Our technique is automatic, but we do not support object splitting in our current system.

Intra-object locality can be improved by grouping hot fields together so that they will usually lie in the same cache line, and it is most useful for objects somewhat bigger than a cache line. The size of hot objects in Java benchmarks is close to and rarely exceeds 32 bytes [32], whereas typical L1 cache line sizes are 64 to 128 bytes and L2 line sizes are 64 to 256 bytes. Thus the performance improvement offered by field reordering alone is usually small. Kistler and Franz use an LRU stack to track the temporal affinity of object fields, and they partition and reorder fields based on their affinity graph [47]. They use a mark-sweep collector, where field reordering has no effect on the object order after collection. Chilimbi et al.'s field reordering depends on profiling to generate reordering advice [22]. The programmer then follows the advice to rewrite the code and reorder fields.

Rubin, Bodik, and Chilimbi developed a framework that attempts to pull together much prior work in this area [61]. Their approach involves the following steps. (1) Produce an access trace with instance and field labels. (2) Compress the trace to fit in main memory and include only accesses relevant to a specific cache size and configuration. (3) Compute the objects with the most accesses and misses. (4) Use object properties (e.g., size, field access frequencies, field access correlations) to select optimizations. (5) Perform a hill-climbing search of possible field and object layout schemes, and model misses for each scheme on the compressed trace. Their framework would need significant changes to address moving collectors, and it is practical only as an offline tool. In contrast, we exploit the reordering of objects inherent in copying collection and our online analysis is inexpensive and robust to phase behavior.

## 3.3 Instruction Locality

Numerous researchers have studied the problem of restructuring programs to improve the memory performance of instruction accesses. Much of the early software-based work reduces virtual memory page faults. Some current work also tries to minimize these very expensive faults [70]. However, most recent work focuses on static and dynamic approaches for reordering code to reduce instruction cache and ITLB misses with offline and online profiling.

#### 3.3.1 Static code placement

Researchers have explored code placement at compile or link-time at a number of different granularities: for example, at the granularity of basic blocks, groups of basic blocks, or entire procedures. A limitation of these static layout approaches is that they produce a fixed static layout, which as we discussed in Section 1.2, is not suitable for a managed runtime. Furthermore, static schemes must assume that the profile data gathered on a training run is representative of all program executions and miss the opportunities available to a managed runtime of exploiting profile data from the program's current execution.

McFarling [53] uses profile data to lay out code to reduce misses in a direct-mapped instruction cache. His algorithm identifies those parts of a program that could overlap each other in the cache and those that should be placed in non-conflicting addresses.

Pettis and Hansen [58] perform profile-based code placement at all three granularities. 1) At the finest granularity, basic block positioning lays out basic blocks to straighten out common control paths and minimize control transfers.

2) Procedure splitting moves a procedure's never-executed basic blocks into a different allocation area from that of its other blocks. 3) At the coarsest granularity, a greedy algorithm starts with an undirected weighted call graph constructed from the profile data and progressively combines its nodes to place frequent caller-callee procedure pairs close together. Pettis and Hansen show that combining all three optimizations can improve performance up to 26% (average about 12%) with a 16 KB directly-mapped unified cache. However, the improvement they achieve is very sensitive to cache organization and their algorithms can not achieve similar improvement on current architectures with bigger cache size (see Section 6.3.4). Because it is both simple and effective,

their procedure ordering algorithm is generally considered the reference placement technique. It is the basis for several more recent algorithms. However, it has performance instability because small changes in the profile data often produce substantially different layouts as we will show in Section 6.3.

Cohn et al [29] describe the Spike post-link optimizer for Alpha/NT executables which includes the Pettis-Hansen procedure code layout algorithm. They report that, on a set of large benchmarks, Spike speeds up most by at least 5%, and often 10% or better. Ispike [52] is a post-link optimizer for the Itanium Process Family (IPF). It uses the IPF performance counters to collect low cost detailed profile information for instruction and data optimizations including inlining, branch forwarding, layout, and prefetching of both code and data. Their code layout optimization includes 1) basic-block chaining to lay out basic blocks in sequence if there is a frequently-executed control flow edge between them, 2) procedure splitting, and 3) procedure layout that keeps hot procedures close together. On a set of small benchmarks, they found that code layout by itself helps one-third of the benchmarks by over 4%.

Hashemi et al. [37] take the cache configuration into account to lay out procedures using cache line coloring. Their algorithm colors each cache line in the instruction cache and uses a greedy algorithm similar to Pettis and Hansen's to place procedures such that the most frequent caller-callee pairs will not occupy the same cache lines. In simulation, they achieve 17% lower instruction miss rate than Pettis and Hansen algorithm. Gloy and Smith [36] also compute procedure layouts that reflect the cache configuration. They

collect complete procedure interleaving information that in combination with the cache configuration and procedure sizes, they use to produce a layout that minimizes both cache conflicts and the instruction working set size. By making use of temporal locality information, their technique eliminates more cache conflict misses than Pettis and Hansen.

Ramirez et al. [59] developed a code reordering system, called the Software Trace Cache (STC), to improve the instruction cache hit rate and increase the processor's effective instruction fetch width. Using profile information, STC determines traces (hot basic block paths) then maps the resulting traces into memory locations that minimize cache conflicts. It also makes effective use of instruction cache lines while tending to keep sequentially-executed instructions in order. STC also reserves a region in the instruction cache for hot instructions to avoid conflict misses with cold instructions.

Since these static approaches generate code layouts ahead-of-time, they lose the flexibility of determining layouts using the actual information for a particular run of a program. They also cannot cope with different program phases. The time complexity of these algorithms is too high for a dynamic scheme. For example, Pettis and Hansen's algorithm has a time complexity of  $O(n^3)$ . If we use Pettis and Hansen's algorithm to These limitations make them less useful in the context of virtual machines.

#### 3.3.2 Dynamic code placement

Dynamic schemes for improving instruction locality typically monitor system behavior and apply optimizations at runtime based on that behavior. Chen and Leupen's just-in-time code layout technique places the procedures of Windows applications in the order of their invocation at runtime [20]. Their results show improvements similar to that of the Pettis and Hansen. It also substantially reduces the program's working set size, often by about 50%. Pettis-Hansen's procedure layout also reduces the working set, but because it is a static approach, it is less effective because the procedures executed do not exactly match those of the training run. Chen and Leupen's approach lays out procedures at allocation time, whereas our approach reorders hot procedures during recompilation or after the program's warm-up phase.

Scales' DPP (dynamic procedure placement) system uses runtime information to dynamically lay out procedure code [62]. DPP uses a loader component that is invoked on procedure calls. It copies the code of the called procedure to a new code region, where it will be close to the caller, then fixes up all references to the procedure to refer to the new copy. Because this system supports C and other languages that are not strongly typed, it deals with indirect calls by memory protecting the original code space, so that attempts to call a procedure at its original address result in a trap whose handler then invokes the new copy of that procedure. DPP's overhead is high because of the virtual memory protection traps and the many calls to the DPP loader. The DPP system can restart procedure placement to try to improve the layout, but each restart is expensive due to the overhead of the new loader calls. An extension of DPP supports runtime profiling: at each call to the loader, the call stack is recorded to build a profile of the calls. This information is used

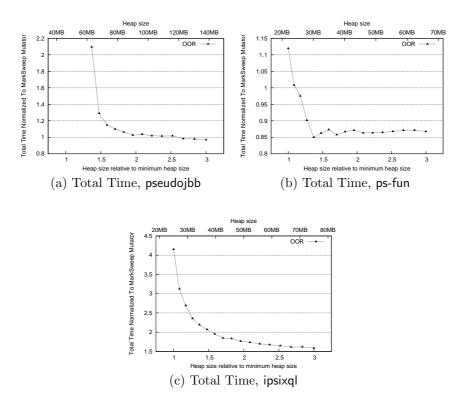

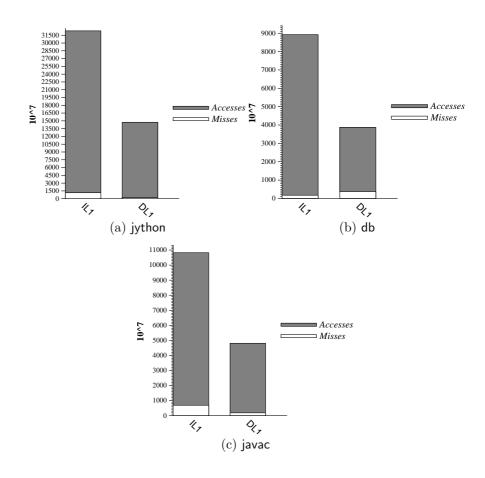

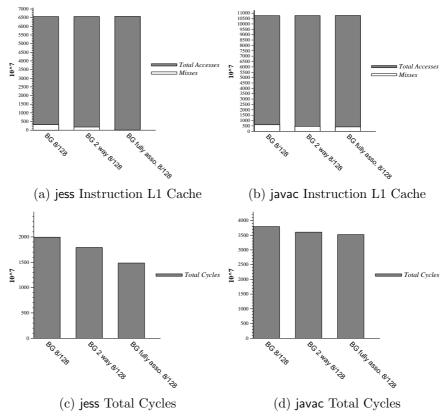

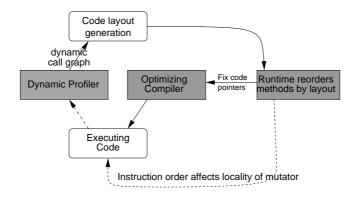

later to improve the layout. However, this profiling is extremely expensive and slows down the program by a factor of ten or more.