Copyright by Jung Woo Ha 2009 The Dissertation Committee for Jung Woo Ha certifies that this is the approved version of the following dissertation:

## Scaling Managed Runtime Systems for Future Multicore Hardware

Committee:

Kathryn S. McKinley, Supervisor

Matthew Arnold

Stephen M. Blackburn

Stephen W. Keckler

Emmett Witchel

## Scaling Managed Runtime Systems for Future Multicore Hardware

by

Jung Woo Ha, B.S.

#### DISSERTATION

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN

December 2009

Dedicated to my wife Songhee.

### Acknowledgments

I would like to express my deepest appreciation for my advisor Kathryn McKinley. Kathryn not only provided me with technical expertise and positive feedback, but she also motivated, inspired, and made the research exciting. Kathryn not only helped me produce a good research output, but she also focused on improving my research skills, and she spent more of her time than was necessary. Kathryn always showed more by example than words. For example, I learned to make the best use of my time and to balance both research and raising kids. I feel very fortunate to be her student.

Steve Blackburn and Matthew Arnold have been enthusiastic supporters, providing lots of good ideas, advice, and helped with writing. They were always available for meetings and discussions, and encouraged me to improve the quality of my research. I am especially grateful to Steve for attending meetings at an inconvenient time in his time zone.

Emmett Witchel advised me in a new research area, and his support was always helpful. Part of my recent research was motivated and influenced from our earlier collaborations. Steve Keckler gave helpful feedback and spent a lot of time reading my thesis and attending talks.

I would also like to thank the graduate students at UT: Mike Bond, Justin Brickell, Katherine Coons, Jason Davis, Maria Jump, Byeongcheol Lee, Bert Maher, Don Porter, Dimitris Prountzos, Christopher Rossbach, Hany Ramadan, Indrajit Roy, Jennifer Sartor, and Suriya Subramaniam. I am grateful for many discussions with them, and that they spent a tremendous amount of time helping to improve my papers and talks.

I would like to thank my wife Songhee for her selfless support. She was tolerant and sacrificed herself by taking care of the family. I could not have completed this work without her excellent support.

## Scaling Managed Runtime Systems for Future Multicore Hardware

Publication No. \_\_\_\_\_

Jung Woo Ha, Ph.D. The University of Texas at Austin, 2009

Supervisor: Kathryn S. McKinley

The exponential improvement in single processor performance has recently come to an end, mainly because clock frequency has reached its limit due to power constraints. Thus, processor manufacturers are choosing to enhance computing capabilities by placing multiple cores into a single chip, which can improve performance given parallel software. This paradigm shift to chip multiprocessors (also called multicore) requires scalable parallel applications that execute tasks on each core, otherwise the additional cores are worthless.

Making an application scalable requires more than simply parallelizing the application code itself. Modern applications are written in *managed languages*, which require automatic memory management, type and memory abstractions, dynamic analysis and just-in-time (JIT) compilation. These managed runtime systems monitor and interact frequently with the executing application. Hence, the managed runtime itself must be scalable, and the instrumentation that monitors the application should not perturb its scalability.

While multicore hardware forces a redesign of managed runtimes for scalability, it also provides opportunities when applications do not fully utilize all of the cores. Using available cores for concurrent helper threads that enhance the software, with debugging, security, and software support will make the runtime itself more capable and more scalable.

This dissertation presents two novel techniques that improve the scalability of managed runtimes by utilizing unused cores. The first technique is a *concurrent dynamic analysis framework* that provides a low-overhead buffering mechanism called *Cache-friendly Asymmetric Buffering (CAB)* that quickly offloads data from the application to helper threads that perform specific dynamic analyses. Our framework minimizes application instrumentation overhead, prevents microarchitectural side-effects, and supports a variety of dynamic analysis clients, ranging from call graph and path profiling to cache simulation. The use of this framework ensures that helper threads perturb the performance of application as little as possible.

Our second technique is *concurrent trace-based just-in-time compilation*, which exploits available cores for the JavaScript runtime. The JavaScript language limits applications to a single-thread, so extra cores are worthless unless they are used by the runtime components. We redesigned a production trace-based JIT compiler to run concurrently with the interpreter, and our technique is the first to improve both responsiveness and throughput in a trace-based JIT compiler.

This thesis presents the design and implementation of both techniques and shows that they improve scalability and core utilization when running applications in managed runtimes. Industry is already adopting our approaches, which demonstrates the urgency of the scalable runtime problem and the utility of these techniques.

# Table of Contents

| Acknow     | wledg  | ments                                                               | $\mathbf{v}$ |

|------------|--------|---------------------------------------------------------------------|--------------|

| Abstra     | ict    |                                                                     | vii          |

| List of    | Table  | 2S                                                                  | xiii         |

| List of    | Figur  | es                                                                  | xiv          |

| Chapte     | er 1.  | Introduction                                                        | 1            |

| 1.1        | Impro  | wing Managed Runtime Systems on Multicore Processors                | 4            |

|            | 1.1.1  | Utilizing Extra Cycles with Helper Threads                          | 4            |

|            | 1.1.2  | Improving Concurrency of Emerging Runtime Systems .                 | 6            |

| 1.2        | Mean   | ing and Impact                                                      | 7            |

| Chapter 2. |        | A Concurrent Dynamic Analysis Framework for Mu<br>ticore Processors | l-<br>9      |

| 2.1        | Relate | ed Work                                                             | 13           |

| 2.2        | Concu  | ırrent Dynamic Analysis Framework                                   | 17           |

|            | 2.2.1  | CAB: Cache-friendly Asymmetric Buffering                            | 19           |

|            |        | 2.2.1.1 Lock-free Synchronization                                   | 20           |

|            |        | 2.2.1.2 Queue Operations                                            | 21           |

|            |        | 2.2.1.3 Optimizing CAB For Multicore Processors                     | 25           |

|            | 2.2.2  | Sampling                                                            | 28           |

|            | 2.2.3  | Interaction with the Garbage Collector                              | 32           |

| 2.3        | A Mo   | del For Analysis Overhead                                           | 32           |

| 2.4        | Threa  | ding Model Impact on Design and Implementation $\ldots$             | 38           |

|            | 2.4.1  | N:M threading model with per-processor CAB $\ . \ . \ .$            | 38           |

|            | 2.4.2  | Native threading model with per-thread CAB                          | 39           |

|            | 2.4.3  | Native threading model with per-processor CAB $\ldots$ .            | 40           |

| 2.5    | Imple         | mentation                                                                                       | 43     |

|--------|---------------|-------------------------------------------------------------------------------------------------|--------|

|        | 2.5.1         | Platform-Specific Implementation Details                                                        | 43     |

|        | 2.5.2         | Dynamic Analyses                                                                                | 50     |

| 2.6    | Evalu         | ation $\ldots$ | 53     |

|        | 2.6.1         | CAB versus Other Buffering Mechanisms                                                           | 56     |

|        | 2.6.2         | Exhaustive Mode Overhead                                                                        | 58     |

|        | 2.6.3         | Buffer Size Scalability                                                                         | 64     |

|        | 2.6.4         | Sampling Mode Accuracy vs Overhead                                                              | 66     |

|        | 2.6.5         | Shared cache and fine-grained parallelism                                                       | 68     |

| 2.7    | Addit         | ional Results                                                                                   | 69     |

| 2.8    | Concl         | usion and Interpretation                                                                        | 70     |

| Chapte | e <b>r 3.</b> | A Concurrent Trace-based JIT Compiler for JavaScr                                               | ipt 76 |

| 3.1    | Relate        | ed Work                                                                                         | 79     |

| 3.2    | Backg         | ground                                                                                          | 81     |

|        | 3.2.1         | Dynamic Typing in JavaScript                                                                    | 81     |

|        | 3.2.2         | Trace-based JIT Compilation                                                                     | 82     |

|        | 3.2.3         | Tamarin and TraceMonkey                                                                         | 84     |

| 3.3    | Desig         | n                                                                                               | 84     |

|        | 3.3.1         | Phase Transitions in TamarinTracing                                                             | 84     |

|        | 3.3.2         | Parallelism to Exploit                                                                          | 88     |

|        | 3.3.3         | Compiled State Variable                                                                         | 89     |

|        | 3.3.4         | Dynamic Trace Stitching                                                                         | 91     |

| 3.4    | Imple         | mentation                                                                                       | 93     |

| 3.5    | Evalu         | ation                                                                                           | 95     |

|        | 3.5.1         | Experiments Setup                                                                               | 95     |

|        | 3.5.2         | SunSpider Benchmarks Characterization                                                           | 96     |

|        | 3.5.3         | Responsiveness                                                                                  | 97     |

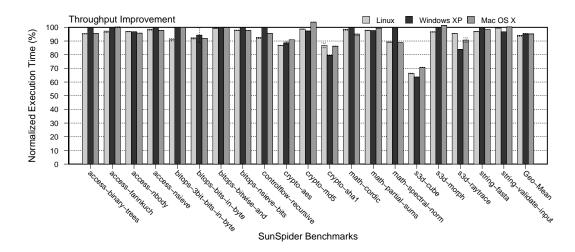

|        | 3.5.4         | Throughput                                                                                      | 100    |

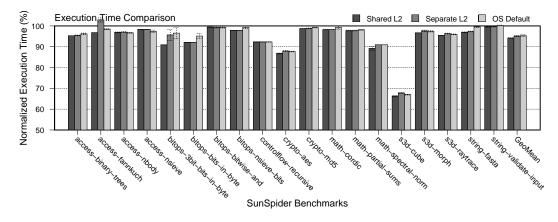

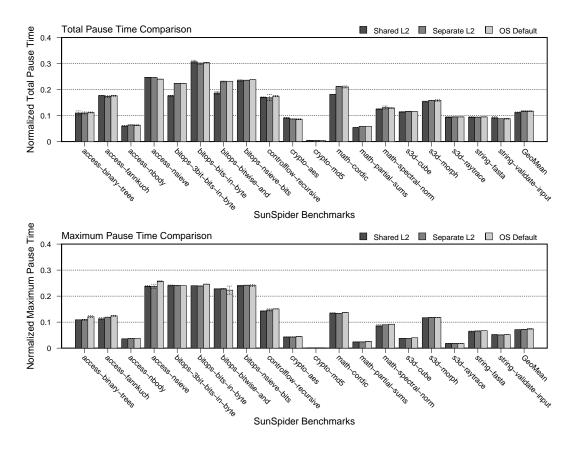

|        | 3.5.5         | Multicore Impact on Performance                                                                 | 101    |

| 3.6    | Concl         | usion and Interpretation                                                                        | 104    |

| Chapter 4. Conclusion | 105 |

|-----------------------|-----|

| 4.1 Future Work       | 106 |

| Bibliography          | 108 |

| Vita                  | 119 |

# List of Tables

| 3.1 | Value of Compiled State Variable<br>(CSV) at a loop header | 91 |

|-----|------------------------------------------------------------|----|

| 3.2 | Workload characterization of SunSpider benchmarks with se- | 05 |

|     | quential Tamarin JIT                                       | 95 |

# List of Figures

| 2.1  | Generic sequential dynamic analysis versus concurrent dynamic analysis.                                                                                                                             | 10 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Cache-friendly Asymmetric Buffering (CAB) in a concurrent dynamic analysis framework.                                                                                                               | 18 |

| 2.3  | Enqueueing and dequeueing pseudo-code                                                                                                                                                               | 21 |

| 2.4  | Experimental processors data cache structure. Instruction or trace cache is omitted. Application and analyzer's mapping to the cores is idealized, and it is not a requirement.                     | 26 |

| 2.5  | Sampling mode. The application does not block and the profiler may use bursty sampling                                                                                                              | 30 |

| 2.6  | Enqueueing and dequeueing pseudo-code for per-processor buffer-<br>ing on native threading model                                                                                                    | 41 |

| 2.7  | x86 assembly code for CAB enqueueing operations. The esi register is used as a base register for the Processor object in Jikes RVM, and eax is a register allocated by the compiler                 | 47 |

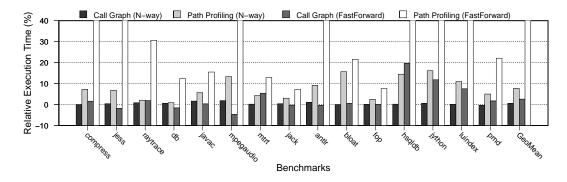

| 2.8  | Performance of N-way buffering and FastForward relative to CAB. We use N:M threading on an Intel Core 2 Quad. The Y-axis is normalized to CAB's execution time.                                     | 56 |

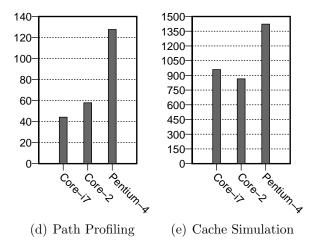

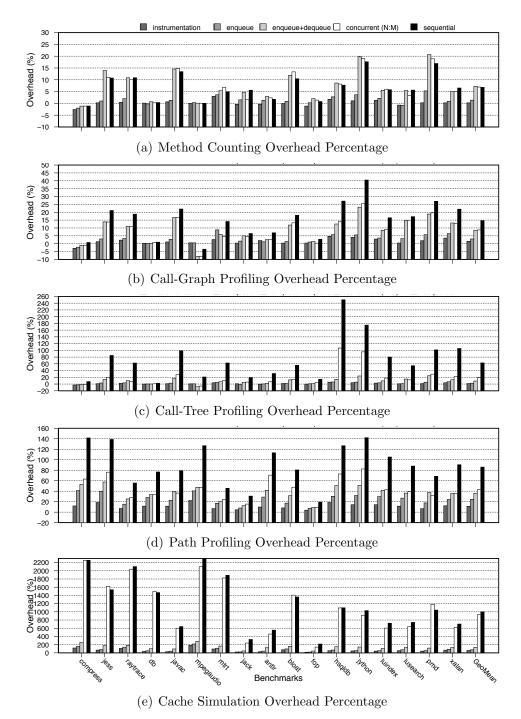

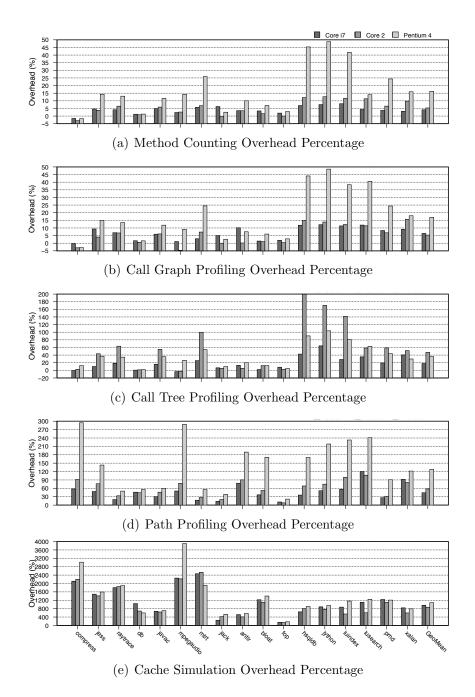

| 2.9  | Exhaustive mode overhead with performance break-down, averaged over all benchmarks (N:M threading model).                                                                                           | 59 |

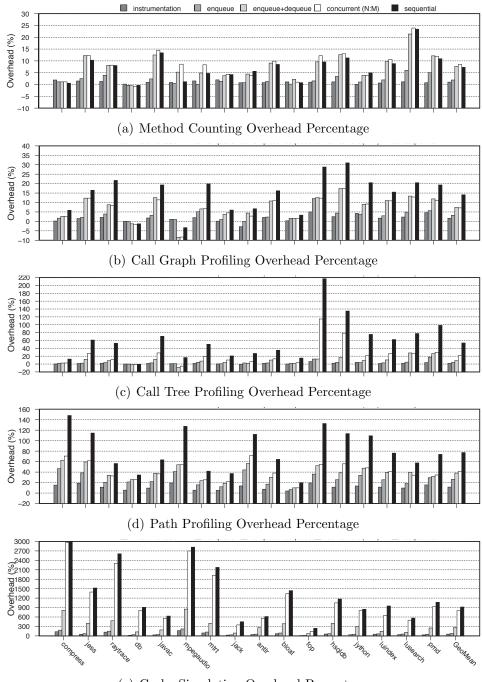

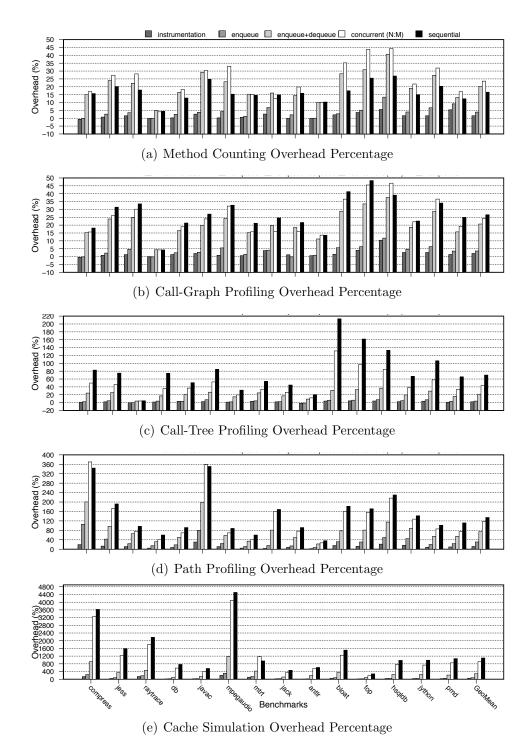

| 2.10 | Exhaustive mode overhead, average over all benchmarks (native threading model with per-thread CAB).                                                                                                 | 62 |

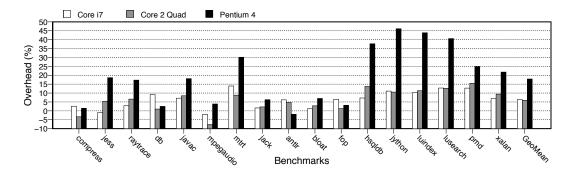

| 2.11 | Call graph profiling overhead on native threading model with per-processor CAB.                                                                                                                     | 63 |

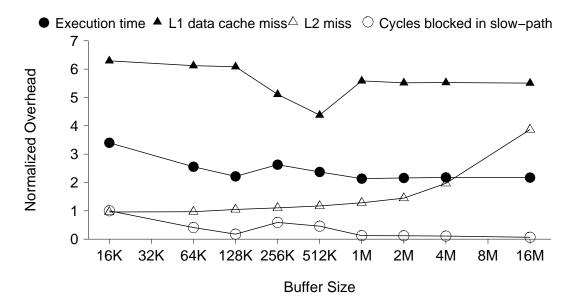

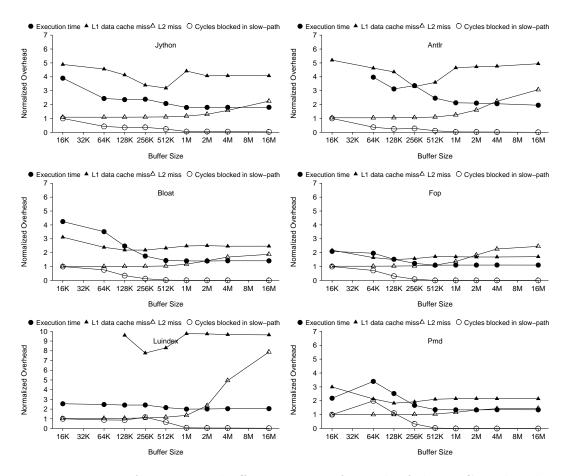

| 2.12 | Performance as buffer size varies for path profiling on DaCapo hsqldb (using N:M threading on an Intel Core 2 Quad).                                                                                | 64 |

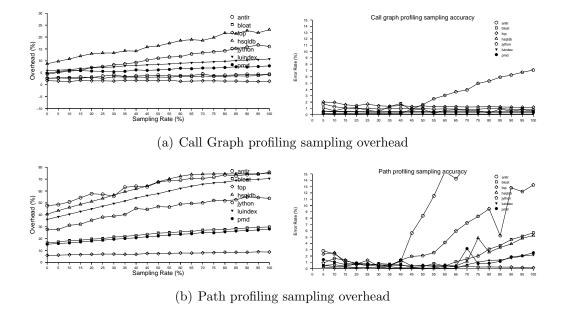

| 2.13 | Sampling overhead and error rate for call graph and path pro-<br>filing (N:M threading on an Intel Core 2 Quad).                                                                                    | 66 |

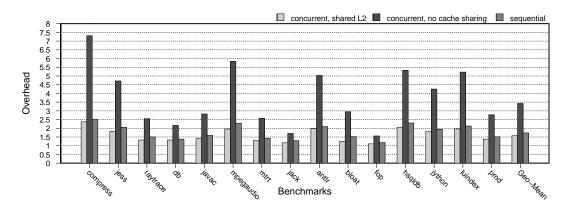

| 2.14 | The importance of shared caches. Path profiling overhead with<br>and without sharing between analyzer and application threads.<br>Note that y-axis is the factor of overhead, and not a percentage. | 68 |

| 2.15 | Per-benchmark exhaustive mode overhead on Core i7 (N:M thread-<br>ing)                                                                                                                              | 71 |

| Per-benchmark exhaustive mode overhead on Core 2 (N:M thread-<br>ing)                                                                                                                                                                                                                                                                                                                   | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Per-benchmark exhaustive mode overhead on Pentium 4 (N:M threading model)                                                                                                                                                                                                                                                                                                               | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Per-benchmark exhaustive mode overhead (native threading).                                                                                                                                                                                                                                                                                                                              | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Performance as buffer size varies for each of the DaCapo bench-<br>marks. Results are for path profiling using N:M threading on<br>an Intel Core 2 Quad                                                                                                                                                                                                                                 | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

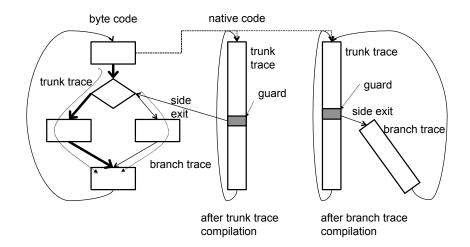

| Byte code and native code transition in the trace-based JIT.<br>Initially, the interpreter interprets on the byte code. First de-<br>tected hot path (thick path) is traced forming a trunk trace.<br>Following hot paths guarded and installed in a side-exit. The<br>compiler attach the branch trace, which begins from the hot<br>side-exit to the loop header, to the trunk trace. | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

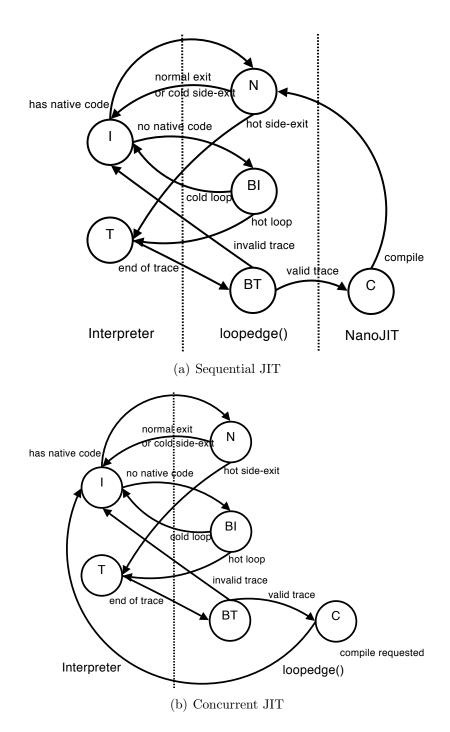

| Phase transitions in Tamarin                                                                                                                                                                                                                                                                                                                                                            | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

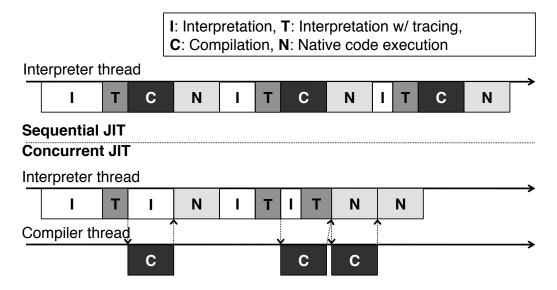

| Example of sequential vs concurrent JIT execution flow                                                                                                                                                                                                                                                                                                                                  | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

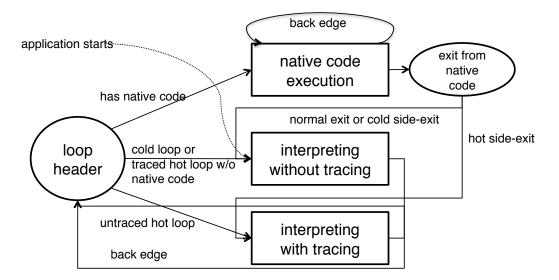

| The interpreter state transition at a loop header                                                                                                                                                                                                                                                                                                                                       | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

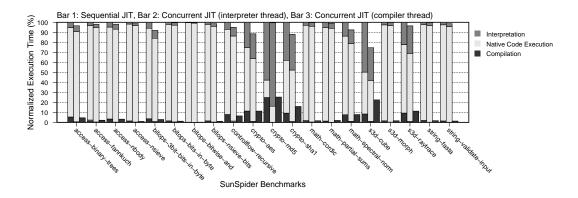

| Average time break down in compilation, native code, and in-<br>terpretation.                                                                                                                                                                                                                                                                                                           | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

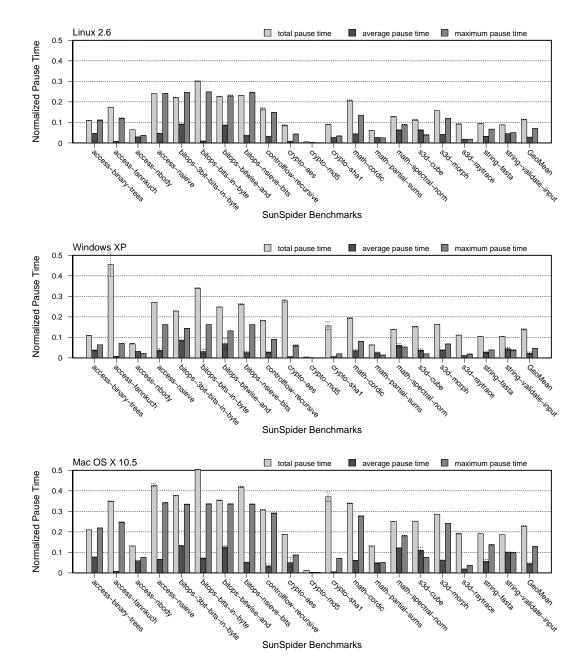

| Pause time ratios of concurrent vs. sequential JITs                                                                                                                                                                                                                                                                                                                                     | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Execution time improvement with concurrent JIT                                                                                                                                                                                                                                                                                                                                          | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Performance impact on various core configurations                                                                                                                                                                                                                                                                                                                                       | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pause time impact on various core configurations                                                                                                                                                                                                                                                                                                                                        | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                         | ing).Per-benchmark exhaustive mode overhead on Pentium 4 (N:M<br>threading model)Per-benchmark exhaustive mode overhead (native threading).Performance as buffer size varies for each of the DaCapo bench-<br>marks. Results are for path profiling using N:M threading on<br>an Intel Core 2 Quad.Byte code and native code transition in the trace-based JIT.<br>Initially, the interpreter interprets on the byte code. First de-<br>tected hot path (thick path) is traced forming a trunk trace.<br>Following hot paths guarded and installed in a side-exit. The<br>compiler attach the branch trace, which begins from the hot<br>side-exit to the loop header, to the trunk trace.Phase transitions in Tamarin.Example of sequential vs concurrent JIT execution flow.Average time break down in compilation, native code, and in-<br>terpretation.Pause time ratios of concurrent vs. sequential JITs.Pause time ratios of concurrent vs. sequential JITs.Performance improvement with concurrent JIT. |

## Chapter 1

### Introduction

Recent trends in modern software towards managed and virtualized programming systems, and trends in hardware towards chip multiprocessor (also known as multicore) have created an immediate and urgent need for (1) parallel applications and (2) runtime systems that are themselves parallel and that can reason about and optimize parallel applications on multicore hardware.

Multicore Hardware Era. Exponential improvements in computer hardware performance over the past few decades have created an ecosystem of ever more capable software that has revolutionized science, communication, entertainment, business, and government. Hardware performance improvements have been mostly the result of scaling up the clock frequency of single processors combined with a sequential and portable software programming model. Sequential programs execute one task at a time. Portable software operates on multiple generations of different hardware platforms. Unfortunately, frequency scaling has reached its limit due to power, wire, and other technology constraints. As a result, hardware vendors are instead seeking to improve performance by putting multiple cores on a single chip. This type of hardware is referred to as *chip multiprocessors* or *multicore*. Multicore processors are already available in the mainstream market and are found in a wide range of computing environments including servers, desktops, mobile, and embedded computers.

Modern Applications Use Managed Runtime Systems. The rapid improvements in processor speed have resulted in programmers more frequently choosing high-level managed sequential languages and programming environments to help them create large, correct, capable, and sequential applications. Managed languages such as Java, JavaScript, Ruby, and C# encourage a modular object-oriented programming style, enforce rich static or dynamic type system, and provide automatic memory management. A managed runtime then performs dynamic analysis, dynamic just-in-time (JIT) compilation, optimization, scheduling, and automatic memory management together with the running application. Managed runtime systems also include dynamic binary translators and hypervisors. Although there are various types of managed runtime systems, they all generally provide applications with rich features such as dynamic optimization [3, 35], dynamic analysis [14], profiling [4], memory management, enhanced debugging, and improved security [47]. Many modern applications run inside a managed runtime system to obtain these benefits.

Challenges and Opportunities of Multicores for Managed Runtime Systems The performance promise of multicore can only be fulfilled when software executes in parallel, and software scalability is now the most important performance concern. It is not possible to improve software performance by increasing the number of cores without application scalability. For managed applications, the whole system, including both the applications and the managed runtime, must be scalable. Parallelizing both the application and each managed runtime component is thus necessary. In particular, communication between the application and the runtime components must be carefully orchestrated to achieve overall scalability. The managed runtime typically interacts with applications through instrumented code, which pauses the application and performs runtime system-level tasks such as dynamic analysis, dynamic compilation, and garbage collection. Many of these components are either fully or partially sequential, because until now, parallel hardware was not widespread, and short frequent communication was sufficiently efficient and exploited memory locality. In the multicore era, redesign of the managed runtime is critical to reduce the pause time incurred by instrumented code and improve application and runtime scalability.

Although multicore hardware presents a scalability challenge to managed runtimes, it also provides new opportunities. When a single application does not fully utilize all available cores, moving or adding managed runtime functionality to concurrent helper threads will hide their overhead. This functionality includes dynamic analysis for performance optimization, debugging, security, and software support. These analyses can collect the necessary data from the application and process it on a separate core perturbing the application less. Such fine-grained helper threads were not practical when processors shared data only through high latency off-chip memory, but multicore processors significantly reduce memory latency by on-chip communication. However, extra cores are not free and the performance of the runtime system is related to microarchitectural factors such as cache configuration and sharing, which require careful design for successful deployment.

In summary, performance on multicore processors require application scalability, which in turn requires scalable managed runtime components. Multicore processors also present new opportunities in the runtime layer. The runtime can enhance existing services and add new ones by using extra cycles with concurrent helper threads.

### 1.1 Improving Managed Runtime Systems on Multicore Processors

We present two novel techniques for enhancing scalability and reducing application overhead using concurrent threads to improve managed runtime systems on multicore processors: (1) a concurrent dynamic analysis framework and (2) a concurrent trace-based JIT compiler.

#### 1.1.1 Utilizing Extra Cycles with Helper Threads

Managed runtime system components perform various dynamic analyses. For example, JIT compilers collect call graph or edge profiling data at runtime, and many data race detectors collect the happens-before relationships of loads and stores. Most of these dynamic analyses are sequential, (i.e., they pause the application thread to perform the analysis) and generally perform sampling to reduce the overhead. However, depending on the analysis, sampling is not always feasible [28], and the sequential part of dynamic analysis reduces the scalability of the application. Our research explores the possibility of executing the analysis concurrently to exploit under-utilized cores and improve scalability. Designing a concurrent analysis scheme is challenging because micro-architectural side-effects and the synchronization between the application and the analysis thread can incur more overhead than sequential analysis.

We introduce a novel *concurrent dynamic analysis framework* to facilitate the implementation of low-overhead concurrent dynamic analysis [25]. The key to our framework is a novel and general producer, consumer communication mechanism, we call *Cache-friendly Asymmetric Buffering (CAB)*. CAB provides a communication channel between the application and the analysis thread so that the application can quickly transfer analysis data off the critical path with minimal overhead. CAB transfers data between the application and analysis thread in a way that proactively prevents micro-architectural side-effects. With our framework, dynamic analysis writers can easily achieve scalability by utilizing extra cycles without having to consider low-level microarchitectural optimization. We show that the CAB communication mechanism is sufficiently general and efficient on a variety of multicore hardware platforms for a wide variety of dynamic analysis problems, from light-weight call graph profiling to path profiling and cache simulation. Our results demonstrate the success of our design as well as the need for careful concurrent communication design.

#### 1.1.2 Improving Concurrency of Emerging Runtime Systems

Industry recently embraced JIT compilation to improve the performance of scripting languages such as JavaScript and ActionScript. Developers are increasingly implementing sophisticated web applications in AJAX (shorthand for asynchronous JavaScript and XML), which uses these scripting languages heavily, and interpretation cannot keep up with the increasing demand for performance. Nonetheless, naively applying traditional methodbased JIT compilation by evolving Java virtual machine technology has not worked, because these languages are dynamically typed. Because the type of an object is determined at run-time, the compiler must either generate machine code for all combinations of types or perform type specialization, neither of which has proven effective.

Recent work has introduced trace-based JIT compilation as an alternative method of type specialization for dynamic languages [18]. Instead of compiling the whole method, trace-based JIT focuses on compiling a hot path within a loop. The interpreter performs loop back-edge profiling, and traces the sequence of instructions on the hot loop path. It only compiles the traced instructions later when they become hot. Naturally, the type of an object is specialized during tracing, which makes the code efficient. Firefox, one of the most popular web browsers, uses this technique, which has proved to be practical.

While trace-based JIT has led to huge performance improvements in JavaScript applications, the performance does not scale on multicore processors because current JavaScript runtimes are all sequential. Because the Java-Script language is sequential – it executes only in one thread, more than one core is useless, unless the managed runtime exploits them. While running a compiler concurrently is trivial for a method-based JIT, previous attempts to make trace-based JIT concurrent have not been successful [17] because of the complex tracing and update states it requires.

We introduce a novel *concurrent trace-based JIT compiler* that executes concurrently with the application on a separate core [27]. Our technique improves application responsiveness because it reduces synchronization with the application to the bare minimum, a single compare and swap. Moreover, the compiler improves the overall throughput because it delivers native code more quickly. While current sequential trace compilers perform a minimal amount of optimization to keep the compilation pause time small, our technique provides an opportunity to reduce the time and improve the code quality without slowing down the application.

#### 1.2 Meaning and Impact

Our concurrent dynamic analysis framework provides the basis for low overhead communication between applications and other managed runtime components, which decouples any micro-architectural optimization from the development of the managed runtime service. Any managed runtime service developer can use our framework to collect data from other cores to design a concurrent service. This framework is not limited to dynamic analyses, but can be applied to any system component that requires offloading data from application instrumented code, such as binary translators and hypervisors. Furthermore, our CAB mechanism is generally applicable to any parallel producer, consumer algorithm that seeks to maximize the performance of the producer.

Both of our techniques have immediate practical impact because they can be deployed now to improve managed runtime scalability. For example, Mozilla, Adobe, and Intel are considering incorporating our concurrent tracebased JIT design principles into their products. ISI East is considering using our concurrent dynamic analysis framework for their mission-critical software.

Software scalability is growing in importance as the number of cores in a processor increases. Use of these techniques and others, such as more scalable and memory efficient garbage collection, are essential to provide a basis for application scalability.

### Chapter 2

## A Concurrent Dynamic Analysis Framework for Multicore Processors

Dynamic analysis is a base technology for performance optimization [1, 12, 45], debugging [29, 39, 44], software support [28, 56], and security [36, 40]. Binary rewriting systems and Just-In-Time (JIT) compilers in managed runtimes need dynamic information about the program to optimize it. They often employ techniques for reducing the overhead, such as sampling, that trade accuracy for performance. However, dynamic analyses used for debugging, software support, and security often require fully accurate analysis. The overhead of more expensive analyses limit their use.

Multicore architectures offer an opportunity to improve the design and performance of dynamic analysis. As the number of cores on commodity hardware continues to increase and application developers are struggling to parallelize application tasks, exploiting unused processors to perform dynamic analysis in parallel with the application becomes an increasingly appealing option.

This chapter explores the design and implementation of a dynamic analysis framework that exploits under-utilized cores by executing analysis

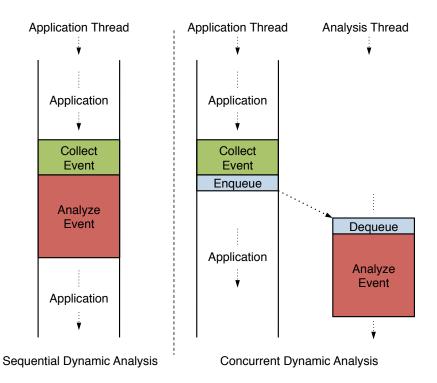

Figure 2.1: Generic sequential dynamic analysis versus concurrent dynamic analysis.

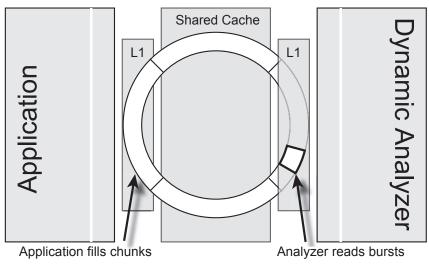

concurrently with the application. In the framework, an application produces events, such as paths executed or memory operations performed, and a separate concurrent analysis thread consumes and analyzes them. Figure 2.1 compares sequential and concurrent dynamic analysis. Whereas traditional dynamic analysis is performed sequentially when the application produces one or a group of events, in our framework, the application queues events in a buffer, and a concurrent analysis thread dequeues and analyzes them.

The ability to communicate data efficiently from one core to another is critical to the success of a concurrent dynamic analysis implementation. Unfortunately, the complexity and variety of multicore architectures and memory hierarchies pose substantial challenges to the design of an efficient communication mechanism. We found that a number of variables influence performance, such as hardware variation, communication costs, bandwidth between cores, false sharing between caches, coherence traffic, and synchronization between the producer and consumer threads.

Our main contribution is a new buffering design that we call *Cache*friendly Asymmetric Buffering (CAB), which provides an efficient mechanism for communicating event data from application threads to analyzer threads on multicore hardware. CAB is asymmetric because we bias the implementation to minimize impact on the application; the application rarely synchronizes with the analysis thread. The design is cache friendly because it exploits shared caches, carefully limits synchronization, and avoids coherence traffic and contention on shared state between private caches.

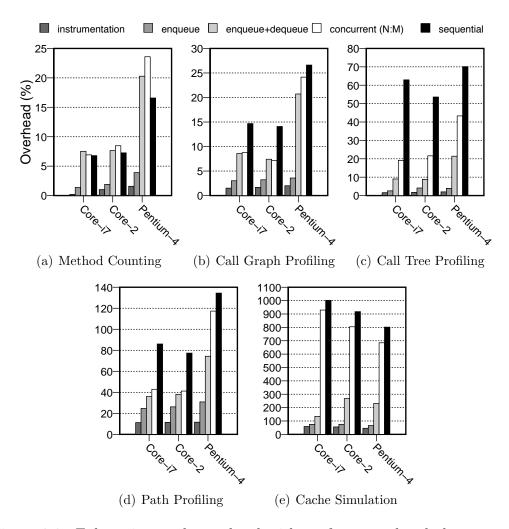

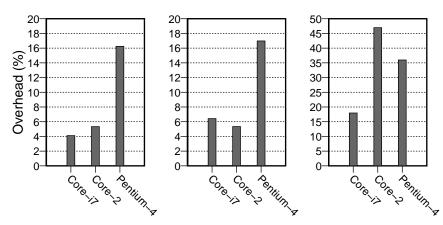

We present the design and implementation of a concurrent dynamic analysis framework that uses CAB as its communication mechanism between the application and analysis. We implement the framework in Jikes RVM [1], a high performance research Java Virtual Machine and perform experiments on three Intel processors with very different cache organizations: Pentium 4, Core 2 Quad, and Core i7. We show that compared to two highly optimized state-of-the-art alternative buffering mechanisms: N-way buffering [57] and FastForward concurrent lock-free queues [22], that CAB reduces overhead for path profiling on average by 8 and 41% respectively. To evaluate the framework, we implement a variety of popular dynamic analyses: *method counting, call graph profiling, call tree profiling, path profiling,* and *cache simulation*. We build and compare sequential and concurrent versions of these analyses.

We demonstrate the framework in an exhaustive mode, for analyses that require fully accurate event records, and in a sampling mode for analyses that can trade accuracy for overhead via sampling. Experimental results for exhaustive mode demonstrate that this framework provides performance improvements for dynamic analysis when the analysis work is greater than the buffering overhead, such as for call graph, call tree, and path profiling. For example, compared to sequential profiling, we reduce the overhead of exhaustive call tree and path profiling between 10 to 70%, depending on the architecture.

In sampling mode, the framework reduces overhead even further. For example, sampling achieves greater than 97% accuracy at a 5% sampling rate, while reducing the overhead by more than half for call graph and path profiling with hsqldb benchmark.

In summary, the contributions of this chapter are as follows.

- The design, implementation, and evaluation of CAB, a novel efficient communication mechanism that is easily tuned for various multicore processors.

- The design, implementation, and evaluation of a novel framework for concurrent dynamic analysis using CAB for exhaustive and sampling

analyses. The framework is analysis-neutral and it is easy to add analyses.

- A demonstration of the framework with a range of analyses: method counting, call graph profiling, call tree profiling, path profiling, and cache simulation.

- A demonstration of the framework with a range of threading model: N:M threading, and native threading.

- A cost model that characterizes dynamic analyses amenable to concurrent implementation and that guides the performance analysis.

We believe that the design issues addressed here transcend the framework as these same issues and solutions are applicable more generally to software design for multicore hardware. The CAB design, which carefully manages communication, coherency traffic, false sharing, and cache residency, offers a building block to future software designers tasked with parallelizing managed runtime services and applications with modest to large communication requirements.

### 2.1 Related Work

We focus here on differences with the most closely related research on dynamic analysis, which exploits parallelism to reduce dynamic analysis overhead.

PiPA (Pipelined Profiling and Analysis) describes a technique for parallelizing dynamic analysis on multicore systems and uses multiple profiling threads per application thread [57]. PiPA is implemented in a dynamic binary translator and collects execution profiles to drive a parallel cache simulator. PiPA uses symmetric N-way buffering and locks to exchange buffers between producers and consumers. Their buffering overhead grows with respect to the size of the buffer, and a small buffer size, e.g., 16KB, achieves the lowest overhead. However, some of their profiling clients require larger buffers for high frequency events. As we show in the results section, CAB is on average 8% faster and up to 16% faster than this organization, and the overhead is consistently low with a large buffer. In our work, the analysis is concurrent (runs in parallel with the application) and parallel (multiple analysis threads run at the same time), but is different from PiPA in that we currently support at most one analysis thread per application thread. This configuration is just for our current implementation, and is not a fundamental limitation of CAB. Our work focuses on efficiently transferring data between cores, and we believe that PiPA would benefit from using CAB.

FastForward is a software-only concurrent lock-free queue implementation for multicore hardware [22]. It uses a sentinel value (NULL) to avoid concurrent access of the queue head and tail indices, and forces a delay between the consumer and producer to avoid cache line thrashing. While their design is reasonable for a general purpose queue, CAB is more suitable for use in concurrent dynamic analysis for two reasons. First, CAB's enqueueing code is more efficient for handling a large number of events, such as those produced by dynamic instrumentation. Second, CAB's dequeueing operation spins only at the beginning of each chunk while FastForward dequeueing operates at a finer granularity, spinning on single events (i.e., one memory location). It thus synchronizes with the producer much more frequently than is necessary with CAB. We compare CAB to FastForward queueing and show that CAB improves performance by 41% on average, and up to 117%.

Shadow Profiling and SuperPin are profiling techniques that fork a shadow process, which runs concurrently with original application process [43, 52]. The shadow process executes instrumented code, while the original application runs uninstrumented. Currently, these approaches are limited to single-threaded applications, because implementations of fork on most thread libraries only fork from the current thread. Unlike our framework, the shadow processes cannot cover the whole program execution, because events around fork and unsafe operations may be lost.

Aftersight decouples profiling at the virtual machine layer using record and replay technology [14]. During one execution of the application, Aftersight uses VM recording to replay execution and then performs profiling on subsequent replayed executions. The profiling executions can be performed concurrently with the recording run, or offline at a later time. In our framework, the application and analysis are decoupled, but the application is executed only once and dynamic analysis is performed online.

Continuous profiling was the first to reduce the profiling overhead due

to micro-architectural side-effects such as cache misses [2]. Continuous profiling collects sampled profile events using hardware performance monitors and interrupts. On every 64k events, the processor raises the interrupt and collects the sample. By using per-processor hash-table, they significantly reduce both synchronization overhead and cache miss penalty, which allows profiling on deployed systems. Most recent processors, support this hardware event-based sampling, and top-notch system event profiling tools such as Intel VTune [15] uses similar event-based sampling. However, this technique is limited to sampling events that are supported by the hardware. Our framework supports both sampling and exhaustive collection, and events need not be determined by the hardware.

Recent work suggests hardware support for low-overhead dynamic analysis. For example, HeapMon uses an extra helper thread to decouple memory bug monitoring [48]. The idea of offloading the data to another thread is similar to our framework. However, HeapMon achieves low-overhead because of hardware buffering and instrumentation support. The hardware support is specifically for heap memory bugs. We achieve performance without any special hardware support, and we assume less about the type of analysis.

iWatcher leverages hardware assisted thread-level speculation to reduce the overhead of monitoring program locations [58]. The platform offers general debugging analysis, but low-overhead is only guaranteed with hardware support. Current multicore processors do not support thread-level speculation.

Our dynamic analysis framework supports both exhaustive and sam-

pling analysis of events. Prior work presented designs for low-overhead sampling of instrumentation [4, 5, 10, 31], where sampling logic is executed in the application thread to determine when a sample should be taken. These approaches are orthogonal and complementary to our work; our framework could perform sampling in the application thread to reduce the amount of data sent to another core. However, our framework also enables a new methodology for sampling, where data is written into a buffer exhaustively and is then optionally consumed (sampled) by the analyzer thread(s). By enabling concurrent execution of the analyzer and the application thread, our technique is likely to outperform traditional sampling techniques when a higher sample rate is used and time in the analyzer increases. However, even with low sample rates this new approach can be beneficial because it moves the sampling logic off the fast path (out of the application thread) and into the analyzer thread. Thus, this new approach is likely to be beneficial if a profiler's communication cost between cores is less than the cost of the sampling logic. CAB reduces communication costs, making this form of sampling more viable.

### 2.2 Concurrent Dynamic Analysis Framework

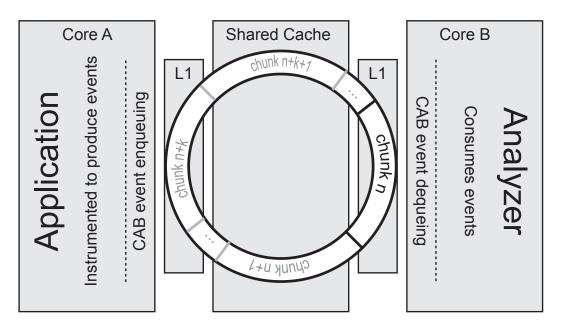

Figure 2.2 shows our software architecture how it is intended to map to modern multicore hardware. Our dynamic analysis system includes an *event producer* (the instrumented application), an *event consumer* (an analyzer), and an *event handling mechanism*, which links the first two. The application and analyzer may be folded together to execute within the same thread, or

Figure 2.2: Cache-friendly Asymmetric Buffering (CAB) in a concurrent dynamic analysis framework.

they may be distinct, executing concurrently in separate threads as shown in Figure 2.1. We focus on the design and implementation of a generic event handling mechanism that supports concurrent dynamic analysis on multicore platforms. The goal of this framework is to exploit underutilized computational resources and fast on-chip communications to minimize the observed overhead of dynamic analysis.

Figure 2.2 also shows the CAB event handling mechanism. An application thread and a dynamic analyzer thread execute on separate cores. The application produces analysis events at injected instrumentation points, and CAB transfers the events to the analysis thread. Since CAB is generic and yet cache-friendly, the analysis writer is: a) freed from low-level micro-

architectural optimization concerns when offloading the event, and b) can implement the analysis logic independently of the application instrumentation.

By constructing a framework, many analyses may reuse the highly tuned mechanisms. The framework is flexible and general. It supports an *exhaustive mode* that collects and analyzes all events, and a *sampling mode*, in which the analysis samples a subset of the events.

#### 2.2.1 CAB: Cache-friendly Asymmetric Buffering

CAB provides a communication channel between application and analysis threads. Two objectives guide the design of CAB: 1) minimizing application instrumentation overhead, and 2) minimizing producer-consumer communication overhead. We use three tactics to address these goals: a) we bias the design toward very low overhead enqueueing, b) we use lock-free synchronization, and c) we partition access to the ring buffer to avoid costly micro-architectural overheads due to cache contention.

At the center of CAB is a single-producer, single-consumer lock-free ring buffer, in which an application thread produces events and an analysis thread consumes them. Since each CAB has only one producer and consumer pair, we can optimize for fast, lock-free access to this shared buffer. Our approach is asymmetric. The application views the buffer as a continuous ring into which it enqueues individual events. By contrast, the analyzer views the buffer as a partitioned ring of fixed sized *chunks*, and each dequeue operation yields an entire chunk. Although producer-consumer algorithms are well studied [22, 37, 41, 42], none of these approaches exploit asymmetry, nor do they consider memory system impact on algorithms. As we show, these CAB features are key to scalable performance on multicore.

#### 2.2.1.1 Lock-free Synchronization

The special case where a communication buffer is shared by just a single producer and a single consumer has the distinct advantage of avoiding intra-producer and intra-consumer coordination, and is well-studied for general purpose concurrent queue implementations [21, 22, 37]. Specifically, the common case enqueue and dequeue operations can be implemented without locks, as wait-free operations [30]. Of course, the operations are not actually wait-free if the desired semantics require that the producer block on a full buffer and the consumer block on an empty buffer. However for dynamic analysis, the common case is high frequency enqueueing and dequeueing, so blocking is exceptional with a reasonably sized buffer. Although requiring CAB to be single producer, single consumer is restrictive, the simplicity and performance of the lock-free implementation it yields is attractive given the importance of minimizing perturbation of the application. However, this does not preclude building a multiple producer or consumer system on top of the lock-free CAB, as discussed in Section 2.4.

```

while (*bufptr != CLEAR) {

1

if (*bufptr == MAGIC)

2

bufptr = &buffer;

// wrap back to start

3

if (*bufptr != CLEAR)

4

block();

// busy, back off

5

6 }

*bufptr++ = data;

// enqueue data

7

(a) Enqueueing events in application code

```

```

block() {

1

spin_wait();

2

pollptr = SKIP(bufptr, CHUNK_SIZE * 2);

3

while (*pollptr != CLEAR) {

4

if (isInvokedGC())

5

// must cooperate

thread_yield();

6

else

7

sleep(n);

8

}

9

}

10

(b) Blocking the application

while (isApplicationRunning()) {

1

```

```

/* keep distance of 2 chunks from producer */

2

index = ((chunk_num + 2) * chunk_size)

3

% buffer_size;

4

while (buffer[index] == CLEAR)

5

spin_or_sleep();

6

/* consume & clear entire chunk */

7

consume_chunk(chunk_num);

8

chunk_num = next(chunk_num)

9

10 }

```

(c) Dequeueing events in analysis code

Figure 2.3: Enqueueing and dequeueing pseudo-code.

#### 2.2.1.2 Queue Operations

CAB can be used for both exhaustive and sampled event collection.

We start by describing queuing operations for exhaustive mode. In exhaustive

mode, every event is enqueued, dequeued, and analyzed.

**Enqueueing** The detailed design of CAB's enqueueing operation is guided by three goals: 1) the design should minimally perturb the application; 2) it needs to accommodate dynamically allocated and dynamically sized event buffers; and 3) if an enqueue operation causes an application thread to block, it must cooperate with the garbage collector and any other scheduling requirements to prevent deadlock.

To minimize perturbation of the application thread, the common case for enqueueing must be fast, and the injection of enqueueing operations should minimally inflate the total code size. Figure 2.3(a) shows the pseudocode for the enqueueing operation. The common case for enqueueing consists of just two lines (1 and 7). When there is space in the buffer, the test at line 1 evaluates to false and execution falls directly through to line 7. The exceptional case may occur either because the end of the buffer has been reached or because the buffer is full. These cases are dealt with by lines 3 and 5 respectively. If the buffer is full, the blocking code in Figure 2.3(b) is executed via a call. Note that all of this code is lock-free, and in the common case, just a single conditional branch is executed (line 1 of Figure 2.3(a)). As shown later in Figure 2.7(a) and Figure 2.7(b), the compiler or binary translator can push lines 2–6 out of the hot code block, keeping the code small and the length of the critical path short.

The control flow in the enqueueing operation depends only on \*bufptr

and two constants: CLEAR and MAGIC (lines 1, 2 and 4 of Figure 2.3(a)). This design is very efficient while also supporting variable sized, dynamically allocated buffers. Dynamic allocation is essential since the number of buffers is established at run-time, and dynamic sizing is valuable since the system may respond to the particular requirements and resource constraints of a given application.

The idea is that the producer will only ever write into buffer fields which have been cleared by the consumer: the producer guards in line 1 of Figure 2.3(a), and the consumer sets the sentinel CLEAR when it consumes the chunk in line 8 of Figure 2.3(c). By using a special sentinel value (MAGIC) to mark the end of the ring buffer, a single test for CLEAR in line 1 will guard against both the end of the buffer being reached (line 2) and a full buffer (line 4). When the end of the buffer is reached, bufptr is reset to point to the start of the buffer, &buffer (line 3). The buffer address is only required in line 3, and is held in a variable. Furthermore, the code path has no explicit test against the buffer size or end of buffer, which is implicitly identified via the MAGIC marker. We can therefore dynamically allocate and size the buffer. This design requires that CLEAR and MAGIC are illegal values for analysis events. In practice, it is easy to choose CLEAR and MAGIC suitably to avoid imposing on the needs of the analyzer.

The exceptional case where the producer thread must block because the buffer is full (line 5) is handled out of line (Figure 2.3(b)). In general, when the producer thread blocks, it must remain preemptible, otherwise it could lead to

deadlock. Specifically, if the consumer invoked a garbage collection while the producer thread was blocked, and the producer thread were unpreemptible, deadlock would ensue. For this reason, the producer thread spins briefly (line 2 of Figure 2.3(b)) before re-testing whether the buffer is full (line 4) and yielding to GC (line 6) or sleeping (line 8). Note that the code checks the contents of pollptr, a point two chunks *ahead* of bufptr (pollptr is set in line 2). By doing this, we effectively back off the producer, giving the consumer time to work and ensuring that upon return there will be at least two chunks of free space available in the buffer.

**Dequeueing** The design of CAB's dequeueing operation is guided by two goals: 1) the design should minimize producer-consumer communication overhead, and 2) similar to enqueueing, it needs to accommodate dynamically allocated and sized buffers. We address the second goal by avoiding any static reference to the buffer address or buffer size, as we described above for enqueueing. To meet the first goal, the analysis thread synchronizes at a coarse grain by consuming a large number of events at once (i.e., a chunk). Furthermore, the design does not induce unnecessary cache coherence traffic on shared or private caches, because CAB never accesses the chunk into which the producer is writing.

CAB prevents the producer and consumer from accessing the same cache lines at once by logically partitioning the ring buffer into large fixed-size chunks, and then ensuring that the consumer remains at least one complete chunk behind the producer (line 5 of Figure 2.3(c)). The size of a chunk is a dynamically configurable option (chunk\_size in Figure 2.3(c)). Recall that the producer is largely oblivious to this partitioning of the ring buffer; it enqueues events regardless of chunk boundaries. However, if the buffer becomes full, the producer waits until there are at least two empty chunks available to it (lines 3 and 4 of Figure 2.3(b)).

In this design, the consumer minimizes overhead and synchronization by dequeueing and processing one chunk at a time (line 8 of Figure 2.3(c)), reducing spinning and checking without affecting the fine-grained producer activity. The analysis happens in the call to consume\_chunk() at line 8. If the analyzer itself is multi-threaded, it may dispatch analysis events to multiple threads. The analyzer clears the buffer immediately after it processes each event as part of consume\_chunk(). Clearing is essential, since it communicates to the producer that the buffer is available (line 1 of Figure 2.3(a)). Clearing immediately after processing each event maximizes temporal locality. In the special case when the producer terminates, it is usually desirable for the consumer to process the remaining entries. Since the consumer normally may not read from the same chunk as the producer, we include in our API the facility for the producer to explicitly flush residual events to the consumer.

#### 2.2.1.3 Optimizing CAB For Multicore Processors

We tune CAB's chunk-based ring buffer design to reduce microarchitectural side-effects due to producer-consumer contention. However, we make

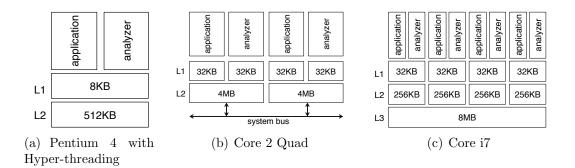

Figure 2.4: Experimental processors data cache structure. Instruction or trace cache is omitted. Application and analyzer's mapping to the cores is idealized, and it is not a requirement.

only minimal assumptions about the multicore architecture. We assume that the hardware can execute multiple software threads simultaneously on separate cores or on the same core. We do not require any specific cache hierarchy. The design works for both private and shared cache designs, but benefits from shared lower-level caches. For example, Figure 2.4 shows three Intel hardware generations, which comprise our experimental platforms. (Section 2.6 has more details on each.) These designs are quite different, yet CAB works well with all of them.

The CAB design ensures that 1) the producer and consumer never access the same cache line simultaneously, 2) the producer and consumer can exploit a shared cache, and 3) the producer and consumer exhibit spatial locality that is amenable to hardware prefetching. The first two design goals avoid cache thrashing, the second also minimizes memory latency, and the third seeks to hide cache miss penalties. To avoid cache thrashing when the producer and consumer do not share an L1 cache, the chunk size should be large enough that by the time the producer is writing to chunk n + 2, chunk n has been fully evicted from the producer's L1 cache. If we assume a strict LRU cache replacement policy, this criteria is satisfied with a chunk size that is greater than or equal to the L1 cache size. In practice, cache replacement policies are not always strict LRU. Thus a larger chunk size is better. Furthermore, since producer-consumer synchronization occur on chunk boundaries, smaller chunks are generally more expensive. Thus, when the producer and consumer share an L1 cache, the synchronization overhead of small chunks still outweighs any locality advantage, which is why large chunks are effective on shared L1 caches as well. This design easily generalizes for more levels of private cache. Our evaluation uses a chunk size of four times the L1 size.

If the runtime uses native threads, we control producer-consumer affinity via the POSIX sched\_setaffinity() API. On the other hand, if the runtime employs a user-level scheduler, we may require modest changes to the scheduler (see Section 2.5.1). We do not require special operating system support or modifications to the operating system's scheduler.

By using a ring buffer, the producer and consumer's memory operations are almost strictly sequential (except when the ring buffer infrequently wraps around). It is hard to test directly the hypothesis that CAB addresses our locality objective, but we measured L1 and L2 miss rates and found that they were not correlated with buffering overhead when we varied the buffer size on both shared and private L1 cache architectures. We also experimented with special Intel non-temporal memory operations but found they degraded performance compared with our straightforward sequential baseline. Worse, the current Intel implementations of non-temporal store operations bypass the entire cache hierarchy, forcing the consumer to go to memory rather than the shared last level cache. CAB would benefit from previously proposed hardware instructions, such as the *evict-me*, or some other mechanism that marks cache lines LRU [38, 53]. CAB could then reduce its cache footprint and thus its influence on the application, while still benefiting from sharing.

## 2.2.2 Sampling

If the analysis thread is unable to keep up with the application, the buffer will eventually fill up and the application thread will block (line 5 of Figure 2.3(a)). Depending on the analysis, this application slowdown may be unavoidable. For example, security analyses and cache simulation profilers typically require fully accurate traces. Other analyses, such as those designed for performance analysis, often tolerate reduced accuracy to gain reduced overhead. In such cases, the profilers in CAB may sample to prevent the application from blocking.

In our sampling framework, the producer still enqueues all the events and then the consumer samples the buffer, analyzing only a subset of the recorded data, skipping over the rest. Other sampling designs, such as timerbased sampling [5], reduce the number of events. However, client analyses that are control-flow-sensitive (e.g., path profiling) and context-sensitive analyses (e.g., call trees), must still insert pervasive instrumentation and maintain their state even if the instrumentation does not store the events. In contrast, our sampling framework eases the burden of implementing these more advanced forms of sampling because the sample decisions are made in the analysis thread; the logic is off the fast path of the application thread so it can be written in a high-level language (rather than inlined into compiled code) and with less concern over efficiency.

**Enqueueing** In sampling mode, the producer *never* checks whether the buffer is full. If the consumer cannot keep up with the producer, the producer simply continues writing to the buffer and data is lost. This design obviously trades accuracy for performance. Figure 2.5(a) shows pseudocode for the application thread when in sampling mode, and should be compared to Figure 2.3(a). The code consists of the minimal instructions required to insert an element into a CAB buffer.

**Dequeueing** Figure 2.5(b) shows pseudocode for dequeueing in sampling mode. Compared to exhaustive mode dequeueing (Figure 2.3(c)), there are two differences. First, each chunk is sampled, according to the value of sampling\_rate (line 8). Second, only the first element in each chunk is cleared (line 10), rather than the entire chunk. We now describe these points in more detail.

```

i if (*bufptr == MAGIC) // end buffer

bufptr = &buffer;

s *bufptr++ = data;

```

(a) Enqueueing pseudo-code for sampling mode.

```

while (isApplicationRunning()) {

1

/* keep distance of 2 chunks from producer */

2