## Software Cache Prefetching for Tracing Garbage Collectors

**Angus Atkinson**

A thesis submitted for the degree of Bachelor of Advanced Computing (Honours) The Australian National University

October 2023

### © Angus Atkinson 2023

This work is released under a Creative Commons Attribution 4.0 International License.

Except where otherwise indicated, this thesis is my own original work. Angus Atkinson 31 October 2023

### Acknowledgements

Firstly, I would like to thank Professor Steve Blackburn, my supervisor and mentor. Thank you for taking a chance on an inexperienced first year back in 2020, for teaching me about garbage collection and for spawning my interest in computer systems, which has guided my degree and future career path. Thank you for accepting me back into the research group for my Honours year, for giving me your time, guidance, and ideas, and for your never-ending patience. Thank you for teaching me the principles of being a good researcher, a good computer scientist and good communicator - the lessons I have learned will serve me well throughout the rest of my career.

Thank you to the rest of the MMTk research group - Zixian Cai, Claire Huang, Yi Lin, Tianle Qui, Kunal Sareen, Eduardo Souza, Kunshan Wang, and Wenyu Zhao - for showing me the ropes, helping me understand the MMTk codebase, and for letting me reserve all of our most important machines for weeks on end for my final performance tests.

I am thankful for the support of those around me over the years. Thank you to my family - Sandra, Bruce and Yolande Atkinson - for listening to all the latenight rants and my fruitless attempts to explain my research to you. Thank you to Peter Oslington for helping me understand Intel's poorly documented performance counters, and the endless thought provoking discussions on each of our research projects. Thank you to my other close friends - Taskil Dastoor, Kieran Hammond, Gemma O'Kane, and Katerina Simeonoff - for all of the dinner parties, D&D sessions and MarioKart races. They have really helped me stay sane throughout my honours year.

Finally, I would like to thank the Tuckwell Scholarship program for their generous financial support and mentorship throughout my entire degree.

### **Abstract**

Garbage collection (GC) is a core component of almost all modern memory safe programming languages. The tracing loop is one of the largest costs in tracing garbage collectors, constituting a significant portion of total collection time. Furthermore, many reference counting collectors rely on tracing to break cycles. Therefore improving tracing performance is paramount to reducing the cost of garbage collection.

Despite the high cost of the tracing loop, there has been little research on how the structure of the loop itself affects tracing performance. Whilst previous work has identified performance differences between Node- and Edge-ordered enqueueing, other design choices have not been explored in great detail, including the queue item type and dual-queueing variants.

One of the primary contributors to the cost of tracing is the poor cache locality of traversing the heap. Software cache prefetching has been identified as one technique for improving the speed of tracing garbage collectors by reducing cache misses. However, in order for it to be an effective optimisation, software cache prefetching needs to be constantly re-evaluated, as rapidly-evolving modern hardware presents a moving target. With the last research on the topic being over a decade old, this technique is long overdue for a revisit. Furthermore, exploring new tracing loop structures could reveal previously unexplored software prefetching opportunities, which could lead to further performance gains.

This thesis explores how the performance of production tracing garbage collectors can be improved by choosing the tracing loop structure that enables the most effective software prefetching. It provides three key contributions: (i) a novel framework for evaluating variations on the tracing loop of garbage collection algorithms, which I call *auxiliary tracing*; (ii) a taxonomy for classifying tracing loop designs, alongside performance evaluations of seven possible structural variations; (iii) a comprehensive performance evaluation of software cache prefetching techniques when applied to the tracing loop of garbage collectors. I conduct my studies in the context of real-world benchmarks on modern hardware (including recent CPU microarchitectures).

My results show that the *Edge-ObjRef* loop (which performs edge-ordered enqueueing of object references) is the highest-performing tracing loop design, yielding an 8.3% performance improvement on AMD Zen 4, and a 15.6% improvement on Intel Coffee Lake, with respect to the default MMTk tracing loop implementation. Furthermore, the *Edge-ObjRef* algorithm demonstrates an 8.1 to 11.1% performance advantage over the canonical tracing loop design (*Node-ObjRef*), despite requiring 2.6 times as many queueing operations on average.

Furthermore, I demonstrate that software cache prefetching consistently increases tracing speed across a wide variety of benchmarks. On Zen 4, the addition of prefetching boosts the performance of the Edge-ObjRef and Node-ObjRef tracing loops by

10.7% and 15.1% respectively, reducing the performance gap but still leaving Edge-ObjRef as a clear winner. On Coffee Lake, the Edge-ObjRef design does not benefit as much from prefetching, allowing the optimised Node-ObjRef algorithm to perform 2.2% better on average.

This work fills a major gap in our understanding of the performance characteristics of tracing loops in garbage collectors. It enables language designers and implementers to make informed choices about the structure of the core tracing loop, regardless of the constraints of their collector (whether it be non-moving or copying). My in-depth analysis of numerous prefetching strategies shows high potential performance improvements, but also highlights the microarchitectural sensitivity of prefetching, demonstrating a need for hardware-specific tuning. Furthermore, my research demonstrates the power and flexibility of the auxiliary tracing framework as a tool for evaluating changes to the core tracing loop.

## **Contents**

| A  | cknov  | wledgements                                       | vii |

|----|--------|---------------------------------------------------|-----|

| A۱ | bstrac | ct                                                | ix  |

| 1  | Intr   | roduction                                         | 1   |

|    | 1.1    | Thesis Statement                                  | 2   |

|    | 1.2    | Contributions                                     | 2   |

|    | 1.3    | Thesis Structure                                  | 3   |

| 2  | Bac    | kground                                           | 5   |

|    | 2.1    | Garbage Collection Terminology                    | 5   |

|    |        | 2.1.1 Tracing Garbage Collection                  | 6   |

|    | 2.2    | MMTk                                              | 8   |

|    | 2.3    | Cache Prefetching                                 | 8   |

|    |        | 2.3.1 Hardware Prefetching                        | 9   |

|    |        | 2.3.2 Software Prefetching                        | 10  |

|    | 2.4    | Summary                                           | 10  |

| 3  | Rela   | ated Work                                         | 13  |

|    | 3.1    | Software Cache Prefetching for Garbage Collection | 13  |

|    |        | 3.1.1 Applications to Tracing Garbage Collection  | 13  |

|    |        | 3.1.2 Other Applications to Garbage Collection    | 16  |

|    |        | 3.1.3 Reflection on Prior Work                    | 16  |

|    | 3.2    | Software Cache Prefetching in OpenJDK             | 17  |

|    |        | 3.2.1 Overview of OpenJDK Prefetching             | 17  |

|    |        | 3.2.2 Evaluation                                  | 18  |

|    | 3.3    | Summary                                           | 20  |

| 4  | Aux    | ciliary Tracing                                   | 21  |

|    | 4.1    | Introduction                                      | 21  |

|    | 4.2    | Design and Implementation                         | 23  |

|    | 4.3    | Validation                                        | 24  |

|    |        | 4.3.1 Experimental Methodology                    | 25  |

|    |        | 4.3.2 Validation of Correctness                   | 27  |

|    |        | 4.3.3 Validation of Performance                   | 28  |

|    | 4.4    | Case Study: Comparison of Heap Layouts            | 29  |

|    | 4.5    | Case Study: Alignment Encoding                    | 31  |

**xii** Contents

|   |            | 7.2.7 More Tracing Loop Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64        |

|---|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   |            | 7.2.6 Prefetching for Other Types of Garbage Collection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63<br>64  |

|   |            | <ul><li>7.2.4 Relationships Between Scanning Techniques and Prefetching</li><li>7.2.5 Hardware Prefetchers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |

|   |            | 7.2.3 Further Evaluation on Different (Micro)architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

|   |            | 7.2.2 Copying and Concurrent Garbage Collectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

|   |            | 7.2.1 Implementation into MMTk's Tracing Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |

|   | 7.1<br>7.2 | Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |

| 7 |            | clusion & Future Work  Concluding Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>61</b> |

|   | 0.0        | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39        |

|   | 6.5<br>6.6 | Write Prefetching for Metadata                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 57<br>59  |

|   | 6.4        | Prefetch Locality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55        |

|   |            | 6.3.4 Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

|   |            | 6.3.3 Node-ObjRef                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51        |

|   |            | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51        |

|   | 0.0        | 6.3.1 Edge-Slot-Dual & Edge-Slot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 48        |

|   | 6.3        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47        |

|   | 6.1<br>6.2 | Opportunities for Prefetching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |

| 6 |            | fetching Professional Control of the Profession Control of the Profess | 43        |

|   | 5.4        | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41        |

|   |            | 5.3.2 Enqueued Objects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |

|   | 0.0        | 5.3.1 Performance Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

|   | 5.3        | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39        |

|   |            | 5.2.1 Dual-Queue Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |

|   | 5.2        | Taxonomy of Tracing Loop Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

|   | 5.1        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

| 5 | Stu        | dy of Tracing Loop Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33        |

|   | 4.7        | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32        |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3         |

# **List of Figures**

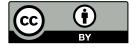

| 2.1                                                         | Slots vs object references                                                                                                                                                                                                                                                                                                                                                                                                 | 7                                            |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

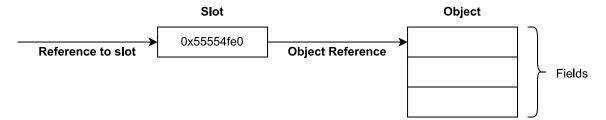

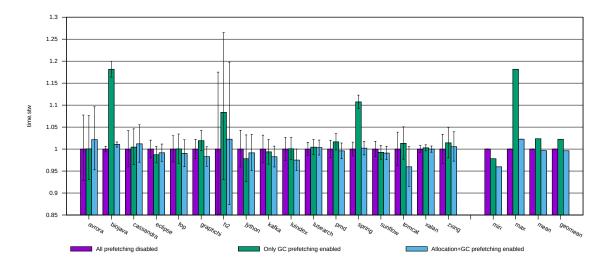

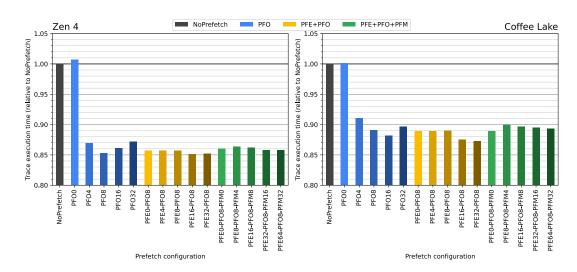

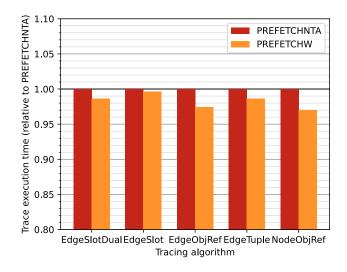

| 3.1<br>3.2                                                  | Comparison of software prefetching options in OpenJDK (Zen 4) Comparison of software prefetching options in OpenJDK (Coffee Lake)                                                                                                                                                                                                                                                                                          | 19<br>19                                     |

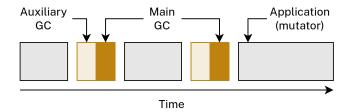

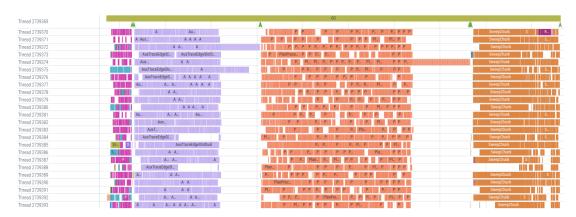

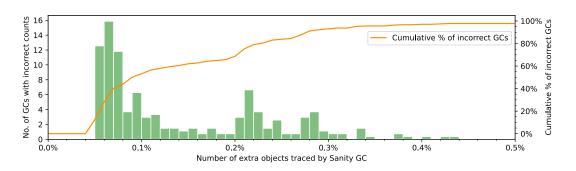

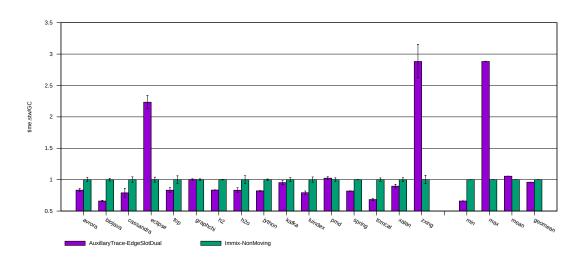

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                      | Timing of the auxiliary trace with respect to the main closure phase Visualisation of the auxiliary trace                                                                                                                                                                                                                                                                                                                  | 22<br>25<br>27<br>29<br>30<br>31             |

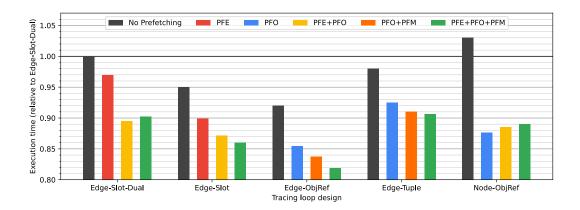

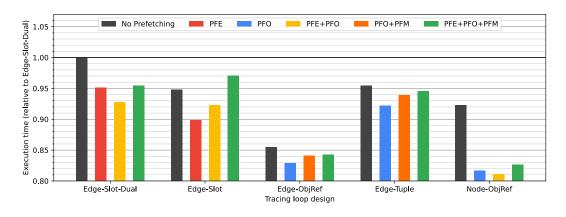

| 5.1<br>5.2<br>5.3                                           | Pseuodocode of six tracing algorithms                                                                                                                                                                                                                                                                                                                                                                                      | 36<br>39<br>40                               |

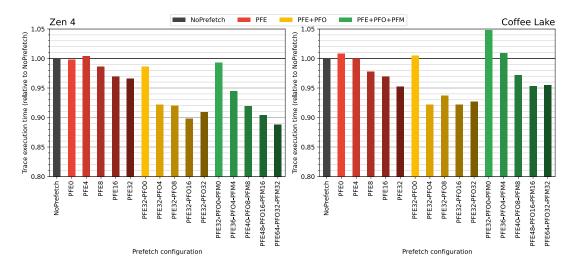

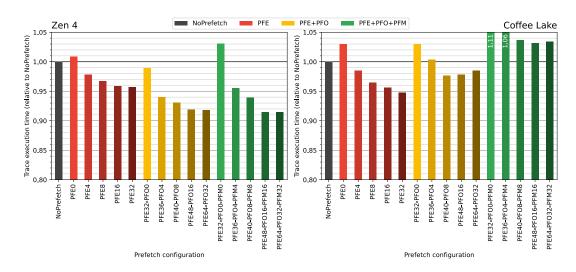

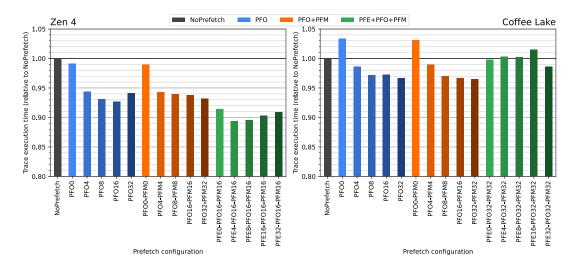

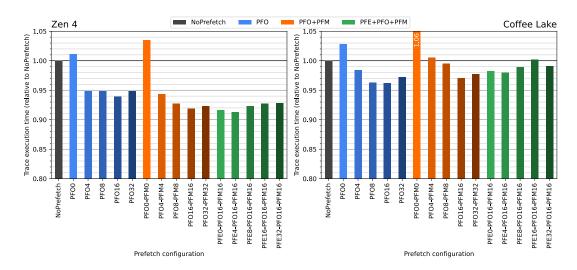

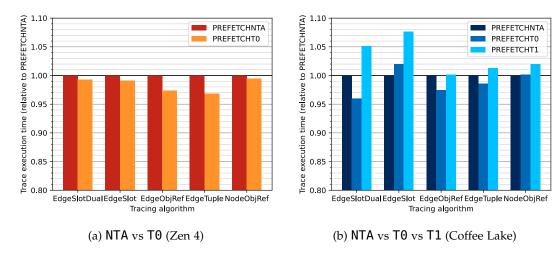

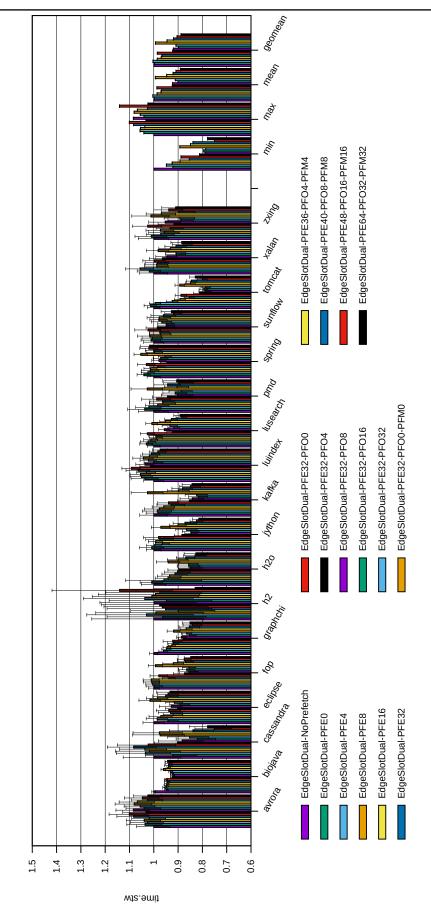

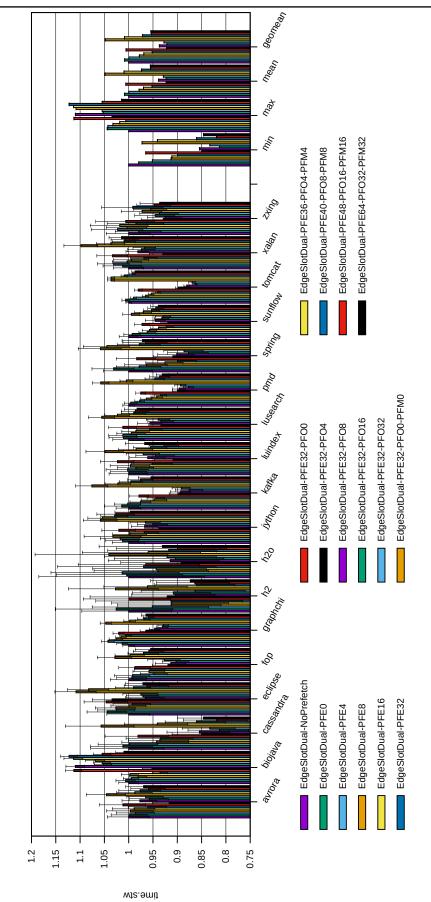

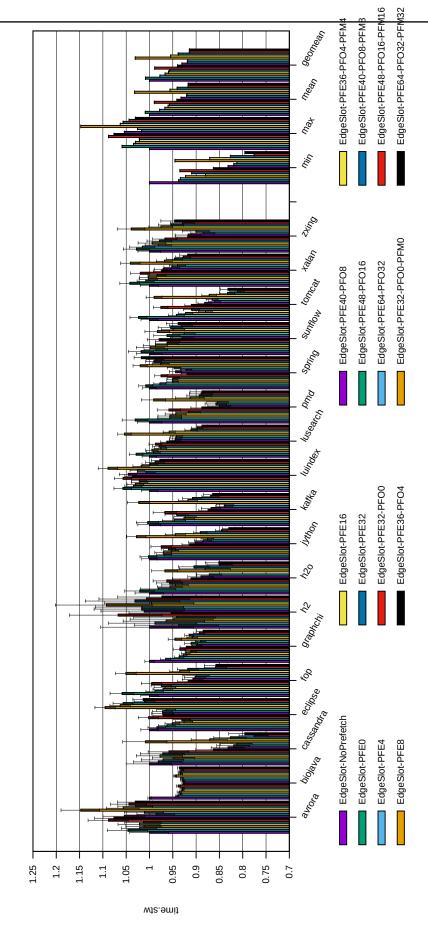

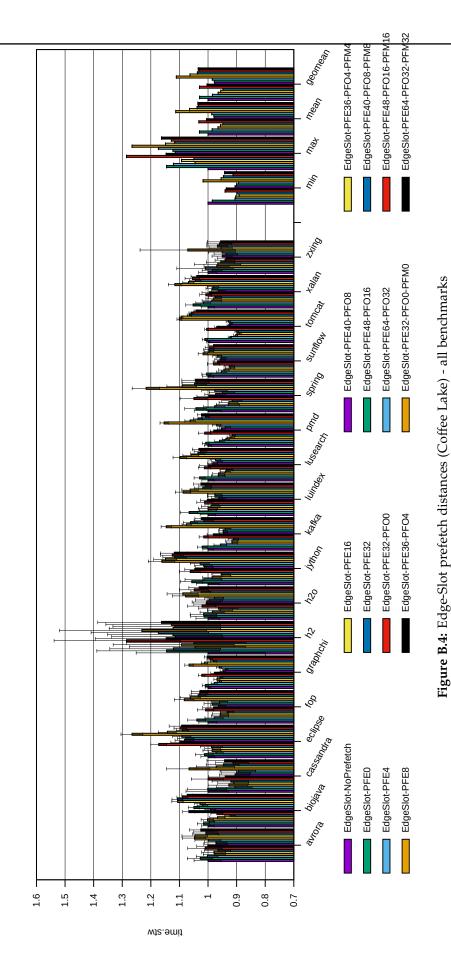

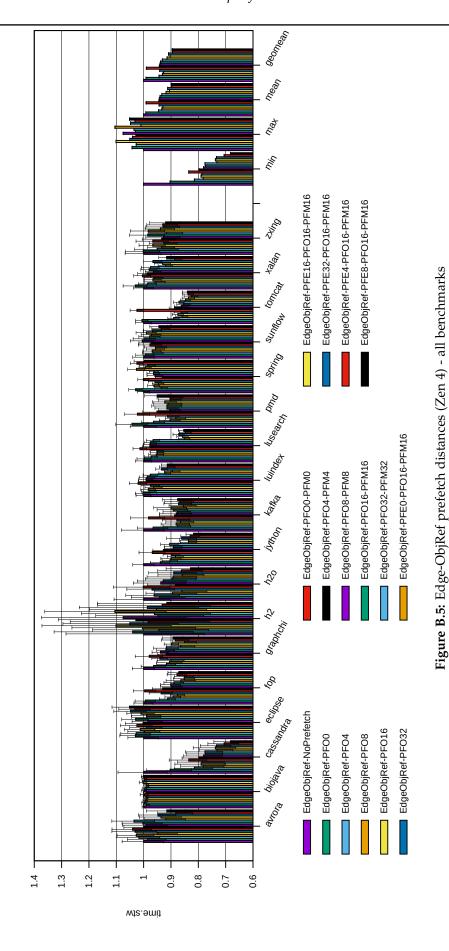

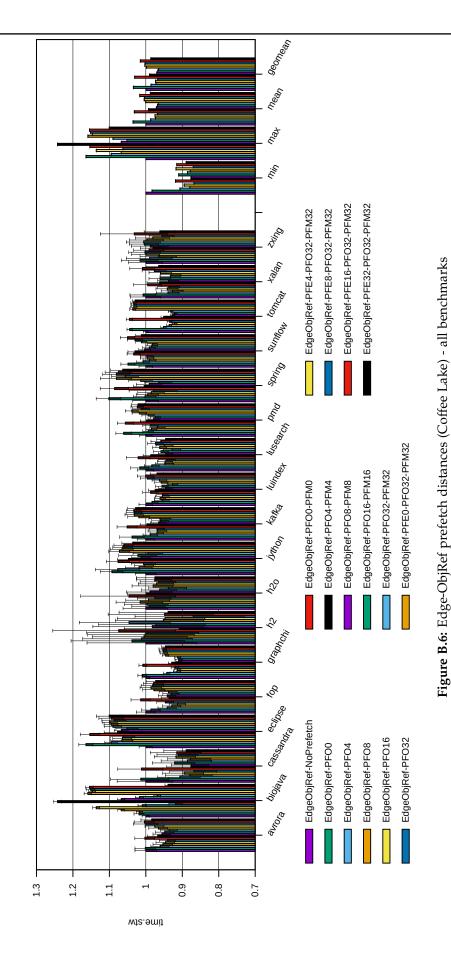

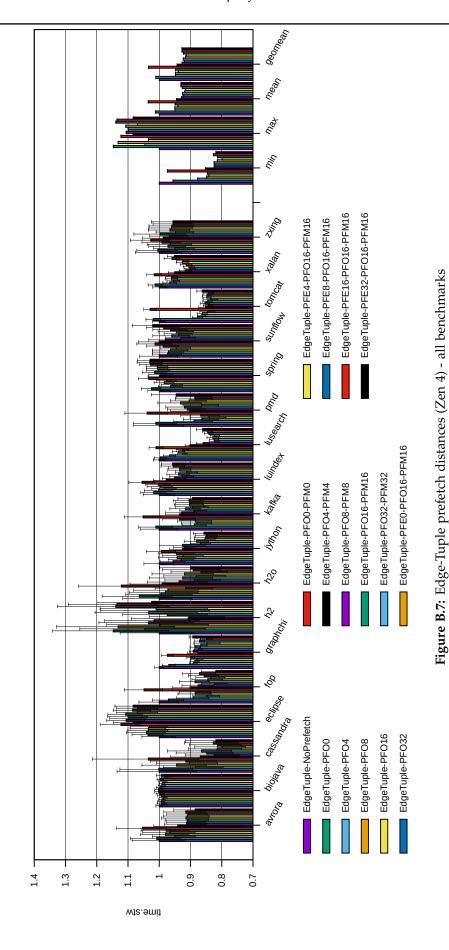

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9 | Edge-Slot-Dual prefetch distances (Zen 4, Coffee Lake) Edge-Slot prefetch distances (Zen 4, Coffee Lake)                                                                                                                                                                                                                                                                                                                   | 49<br>49<br>52<br>52<br>53<br>54<br>54<br>57 |

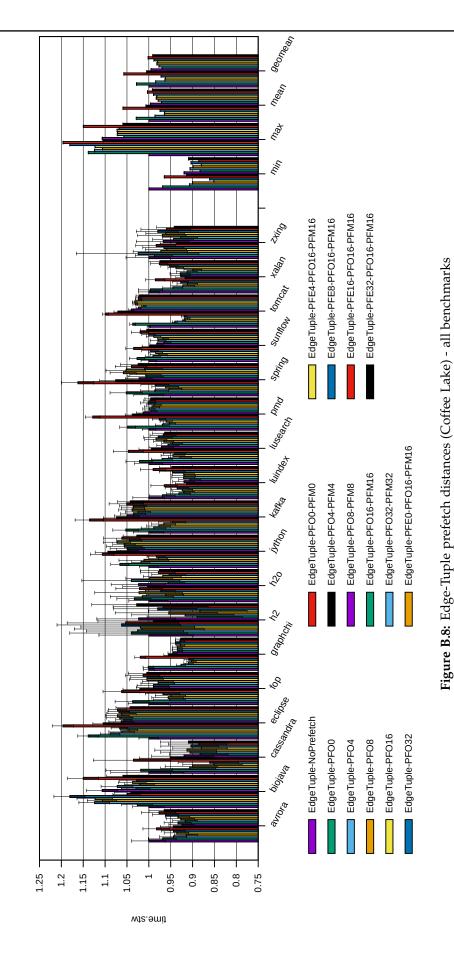

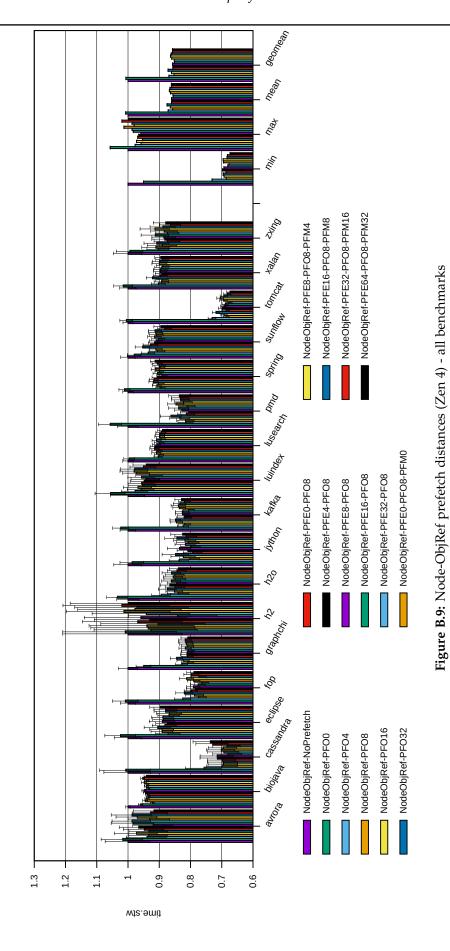

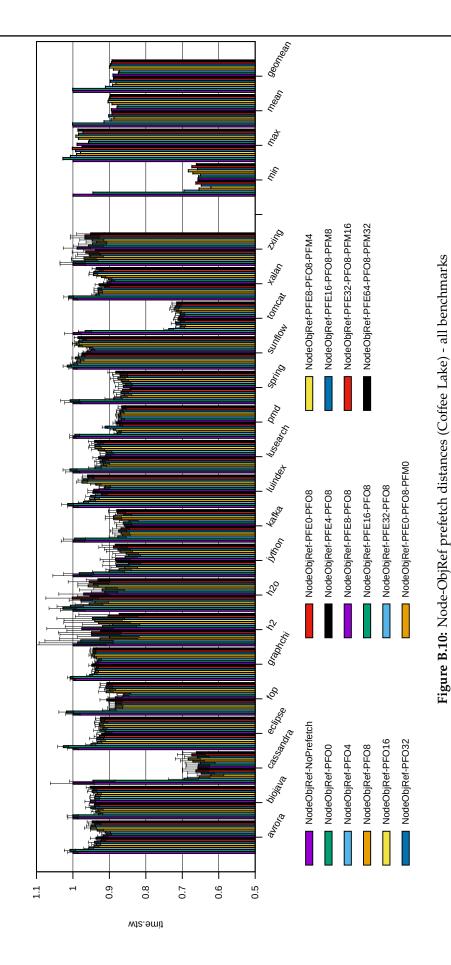

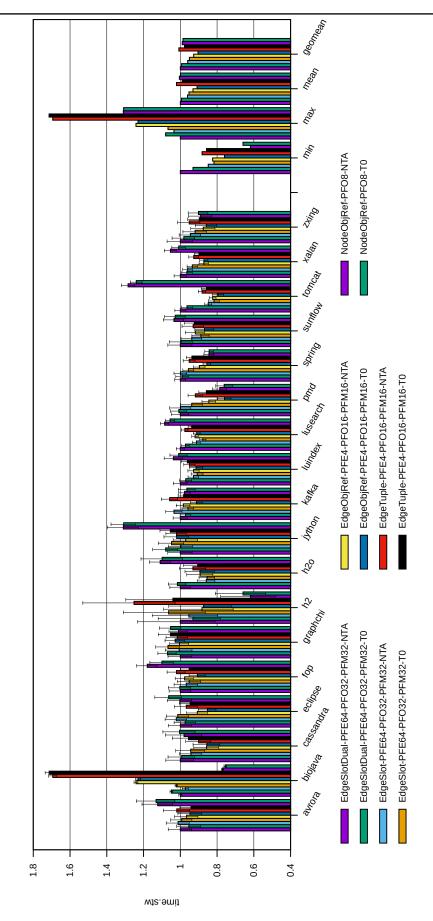

| B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.6<br>B.7<br>B.8        | Edge-Slot-Dual prefetch distances (Zen 4) - all benchmarks Edge-Slot-Dual prefetch distances (Coffee Lake) - all benchmarks Edge-Slot prefetch distances (Zen 4) - all benchmarks Edge-Slot prefetch distances (Coffee Lake) - all benchmarks Edge-ObjRef prefetch distances (Zen 4) - all benchmarks Edge-ObjRef prefetch distances (Coffee Lake) - all benchmarks Edge-Tuple prefetch distances (Zen 4) - all benchmarks | 68<br>69<br>70<br>71<br>72<br>73<br>74<br>75 |

| B.9<br>B.10                                                 | Node-ObjRef prefetch distances (Zen 4) - all benchmarks                                                                                                                                                                                                                                                                                                                                                                    | 76<br>77                                     |

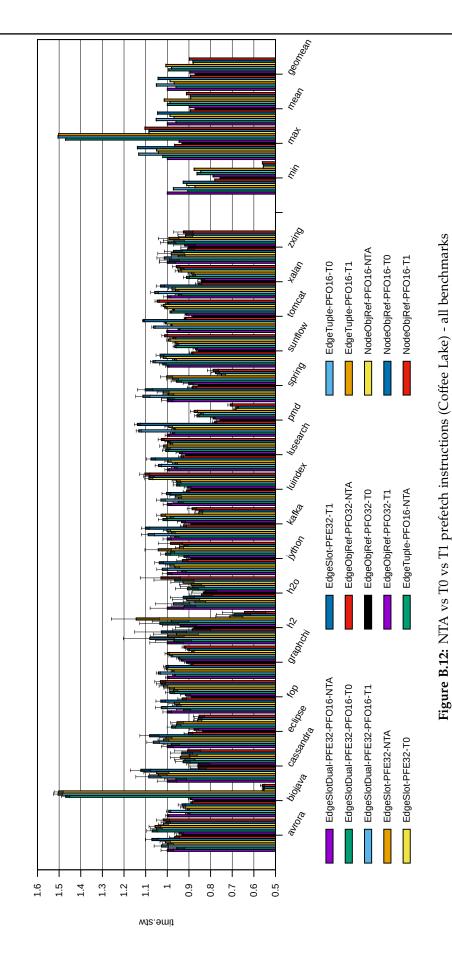

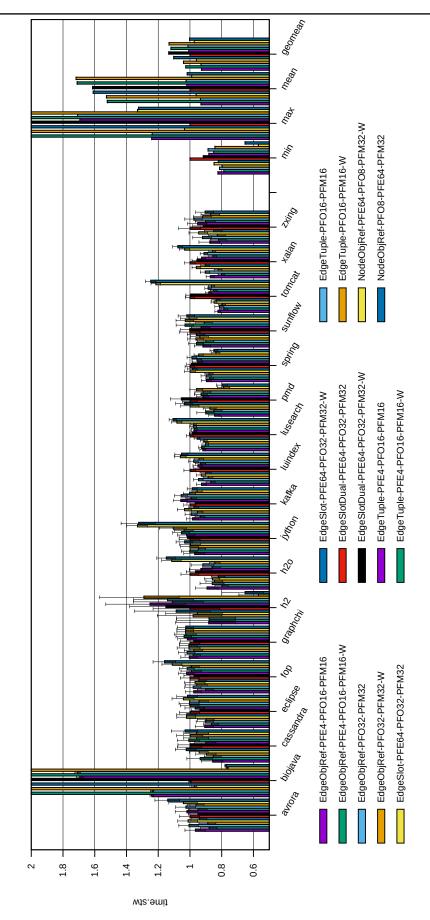

| B.12 NTA vs T0 vs T1 prefetch instructions (Coffee Lake) - all benchmarks . | 79 |

|-----------------------------------------------------------------------------|----|

| B.13 Metadata write prefetching (Zen 4) - all benchmarks                    | 80 |

## **List of Tables**

| 4.1 | Hardware specifications                                     | 26 |

|-----|-------------------------------------------------------------|----|

| 5.1 | Properties of tracing loop designs                          | 38 |

| 6.1 | Prefetching opportunities by tracing loop design            | 45 |

| 6.2 | Microarchitectural implementations of prefetch instructions | 56 |

# Listings

| 4.1 | Work bucket stages for the auxiliary trace                | 24 |

|-----|-----------------------------------------------------------|----|

| 5.1 | The canonical mark-sweep tracing loop                     | 33 |

| 5.2 | Edge enqueueing tracing loop                              | 34 |

| 5.3 | Node-ObjRef                                               | 36 |

| 5.4 | Edge-ObjRef                                               | 36 |

| 5.5 | Node-Slot                                                 | 36 |

| 5.6 | Edge-Slot                                                 | 36 |

| 5.7 | Node-Tuple                                                | 36 |

| 5.8 | Edge-Tuple                                                | 36 |

| 5.9 | Edge-Slot-Dual                                            | 37 |

| 6.1 | Implementation of prefetching on the Address type         | 45 |

| 6.2 | Implementation of object prefetching in Node-ObjRef       | 46 |

| 6.3 | Encoding of prefetch distance in assembly instruction     | 46 |

| A.1 | Implementation of prefetching on the ObjectReference type | 65 |

| A.2 | Implementation of prefetching for metadata                | 65 |

| A.3 | Implementation of prefetching on the Edge trait           | 66 |

xviii LISTINGS

### Introduction

In a world where computer security is paramount, software developers are increasingly choosing to use memory-safe programming languages for their projects. One of the ways that managed languages provide memory safety is through *automatic memory management* of dynamically allocated memory. Apart from the notable example of Rust, almost all modern programming languages use *garbage collection* for memory management.

One of the most common paradigms of garbage collection is *tracing* garbage collection, which involves performing a transitive closure of the heap to identify live objects. Tracing is a core component of many production garbage collectors, including collectors for V8 [Marshall, 2019], Ruby [Ruby Contributors, 2023], and OpenJDK (G1 [Detlefs et al., 2004], Shenandoah [Flood et al., 2016], ZGC [Liden and Karlsson, 2018a,b] and C4 [Tene et al., 2011]). Even modern high-performance reference counting collectors such as RCImmix [Shahriyar et al., 2013] and LXR [Zhao et al., 2022] rely on tracing to collect cycles in the object graph, in order to avoid memory leaks.

The tracing loop is responsible for traversing the object graph, marking and scanning all objects. This makes it one of the most performance-critical aspects of a tracing collector. Previous research has estimated that the tracing loop constitutes as much as 57% [Boehm, 2000], 70% [Cher et al., 2004], or 96% [Garner, 2011] of total collection time - primarily due to the low cache locality of tracing the heap. Despite the high cost of the tracing loop, there has been relatively little research of alternative designs and structural variations which could improve performance. Although some variations on the canonical tracing loop design have been explored, including edge-ordered enqueueing [Garner et al., 2007], other aspects have not been examined in as much detail. This includes enqueuing slots instead of (or in addition to) object references, and dual-queue designs. This thesis explores several new designs and evaluates their effectiveness.

Since the cache locality of the tracing loop is so poor, one other area of previous research has been to introduce software cache prefetching instructions into the loop, to preemptively bring data into cache before it is needed [Boehm, 2000; Cher et al., 2004; Garner et al., 2007]. This technique has been shown to be relatively successful, reducing garbage collection time by up to 20-30%. However, despite the ever-changing nature of modern hardware, these results have not been re-evaluated in a modern

Introduction

context. Furthermore, I believe that exploration of new tracing loop designs could uncover additional opportunities for software cache prefetching that were not possible before, potentially improving tracing performance. Thus, the potential impact of software prefetching in contemporary setting is an open question.

In this thesis, I primarily examine the application of prefetching to the core tracing loop. Other prefetching opportunities in garbage collectors (e.g. for allocation or reference counting) are possible interesting avenues for future research, but are beyond the scope of this thesis.

#### 1.1 Thesis Statement

2

Optimisation of tracing loop performance is critical to reducing the cost of garbage collection. I believe that the performance of production tracing garbage collectors can be improved by choosing the tracing loop structure that enables the most effective software prefetching.

#### 1.2 Contributions

In this thesis, I provide four major contributions:

- 1. I introduce *auxiliary tracing*, a novel evaluation framework which can be used to:

- (a) measure and compare the performance of structural variations on the core tracing loop of garbage collectors;

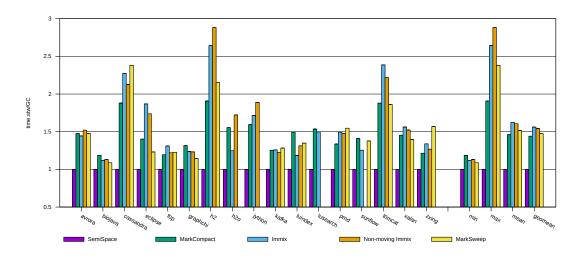

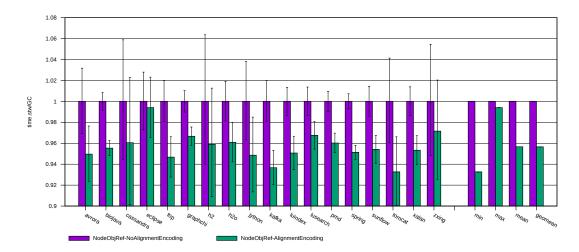

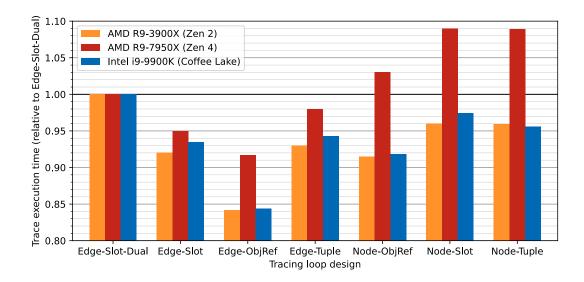

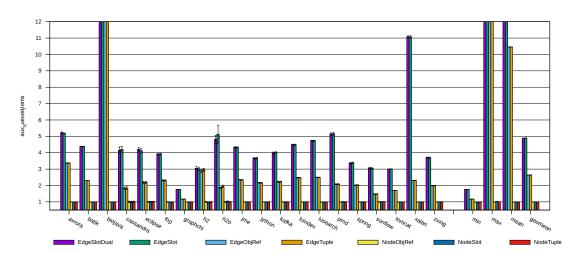

- (b) assess the performance implications of the heap layouts generated by a wide spectrum of garbage collection algorithms;